# UNIVERSIDADE REGIONAL DE BLUMENAU CENTRO DE CIÊNCIAS EXATAS E NATURAIS CURSO DE CIÊNCIAS DA COMPUTAÇÃO

(Bacharelado)

# PROTÓTIPO DE AMBIENTE LADDER PARA OS MICROCONTROLADORES 8051 E PIC16F873

TRABALHO DE CONCLUSÃO DE CURSO SUBMETIDO À UNIVERSIDADE REGIONAL DE BLUMENAU PARA A OBTENÇÃO DOS CRÉDITOS NA DISCIPLINA COM NOME EQUIVALENTE NO CURSO DE CIÊNCIAS DA COMPUTAÇÃO — BACHARELADO

### SIDNEI ALEXANDRE DE ALMEIDA

BLUMENAU, JUNHO/2003

2003/2-23

## PROTÓTIPO DE AMBIENTE LADDER PARA OS MICROCONTROLADORES 8051 E PIC16F873

### SIDNEI ALEXANDRE DE ALMEIDA

ESTE TRABALHO DE CONCLUSÃO DE CURSO, FOI JULGADO ADEQUADO PARA OBTENÇÃO DOS CRÉDITOS NA DISCIPLINA DE TRABALHO DE CONCLUSÃO DE CURSO OBRIGATÓRIA PARA OBTENÇÃO DO TÍTULO DE:

# Prof. Antônio Carlos Tavares — Orientador na FURB Prof. José Roque Voltolini da Silva — Coordenador do TCC BANCA EXAMINADORA Prof. Antônio Carlos Tavares Prof. Mauro Mattos Prof. Miguel Alexandre Wisintainer

### **RESUMO**

Este trabalho apresenta a implementação de um ambiente de linguagem *Ladder*. A partir do diagrama, este ambiente é capaz de gerar código *assembly* para os microcontroladores 8051 e PIC16F873. Para implementação utilizaram-se técnicas de orientação a objeto e técnicas de construção de compiladores.

### **ABSTRACT**

This work describes the implementation of a language Ladder environment. Starting from a diagram, this tool is able to generate source code assembly to microcontrolers 8051 and PIC16F873. The software was built using object orientation techniques and compilers construction techniques.

### **LISTA DE FIGURAS**

| FIGURA 1 -EXEMPLO DE UM DIAGRAMA LADDER                     | 14 |

|-------------------------------------------------------------|----|

| FIGURA 2 - PINAGEM DO MICROCONTROLADOR PIC16F873            | 21 |

| FIGURA 3 -DIAGRAMA DA ARQUITETURA INTERNA DO PIC16F873      | 23 |

| FIGURA 4 – FLUXOGRAMA DA CAPTURA A/D                        | 30 |

| FIGURA 5 - MAPA DA MEMÓRIA DO PIC16F873                     | 33 |

| FIGURA 6 - PINAGEM DO 8051                                  | 34 |

| FIGURA 7 -MAPA DE MEMÓRIA DO 8051                           | 38 |

| FIGURA 8 - DIAGRAMA DE UM COMPILADOR                        | 39 |

| FIGURA 9 - ÁRVORE DA OPERAÇÃO IF (A OR B) AND C THEN Z      | 40 |

| FIGURA 10 – INTERFACE DO MPLAB                              | 44 |

| FIGURA 11 – TELA DE EDIÇÃO DO PROJETO                       | 45 |

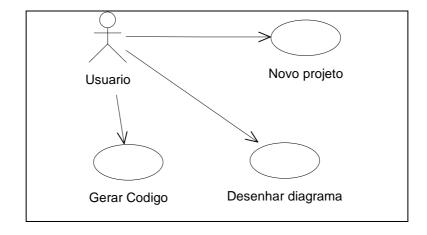

| FIGURA 12 - DIAGRAMA DE CASOS DE USO                        | 46 |

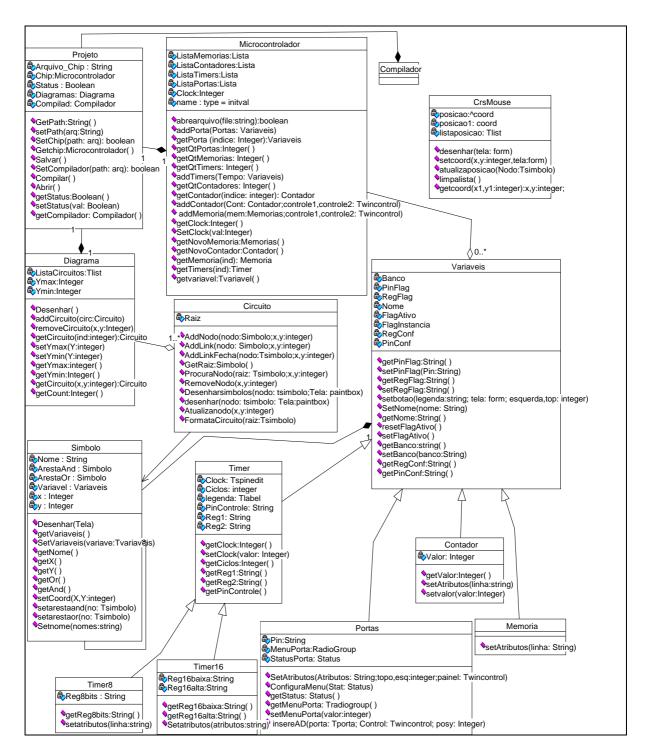

| FIGURA 13 - DIAGRAMA DE CLASSES                             | 47 |

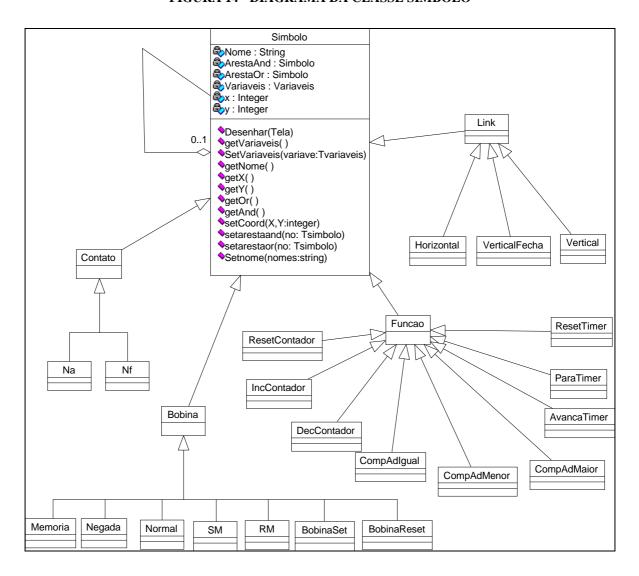

| FIGURA 14 - DIAGRAMA DA CLASSE SÍMBOLO                      | 48 |

| FIGURA 15 - DIAGRAMA DA CLASSE COMPILADOR                   | 49 |

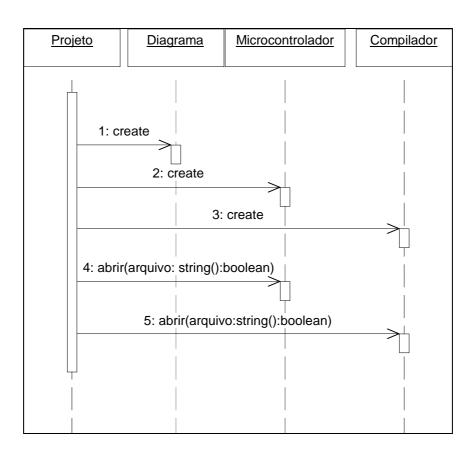

| FIGURA 16 - DIAGRAMA DE SEQÜÊNCIA ESCOLHER MICROCONTROLADOR | 51 |

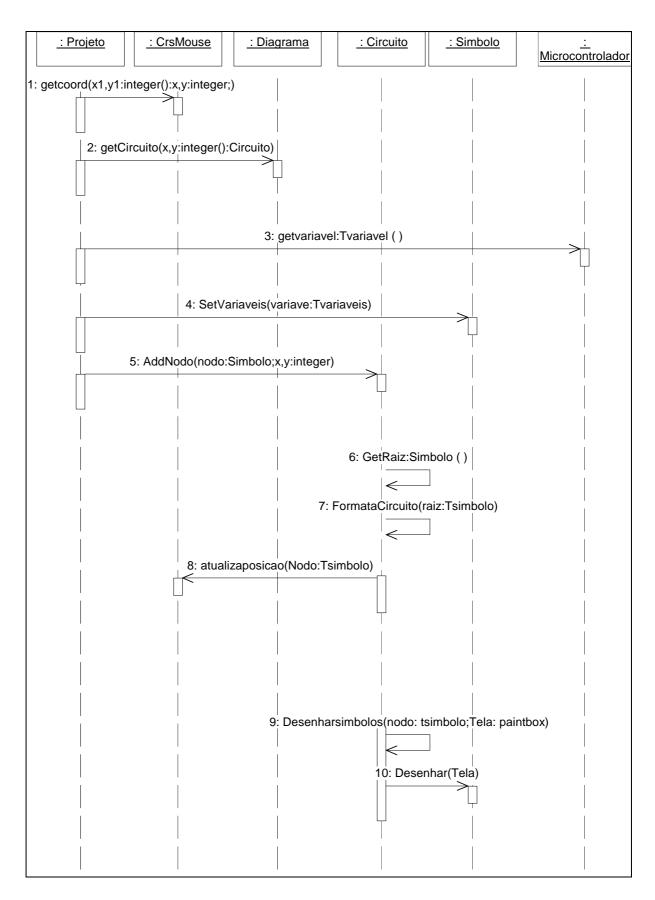

| FIGURA 17 - DIAGRAMA DE SEQUÊNCIA DESENHAR DIAGRAMA         | 52 |

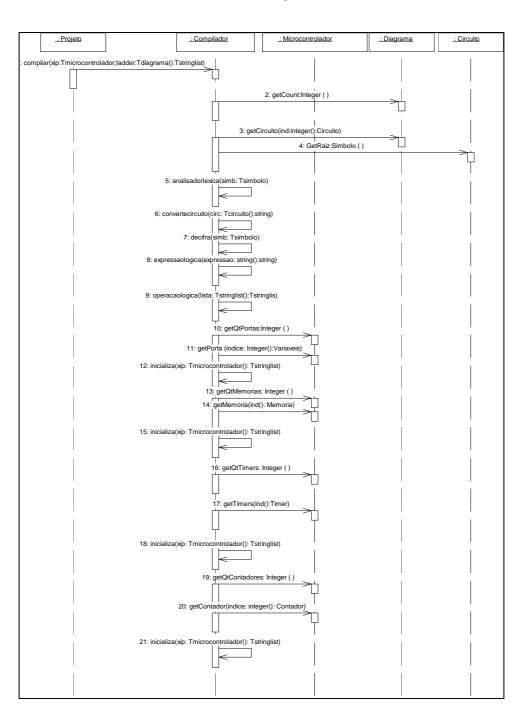

| FIGURA 18 - DIAGRAMA DE SEQÜÊNCIA GERAR CÓDIGO              | 53 |

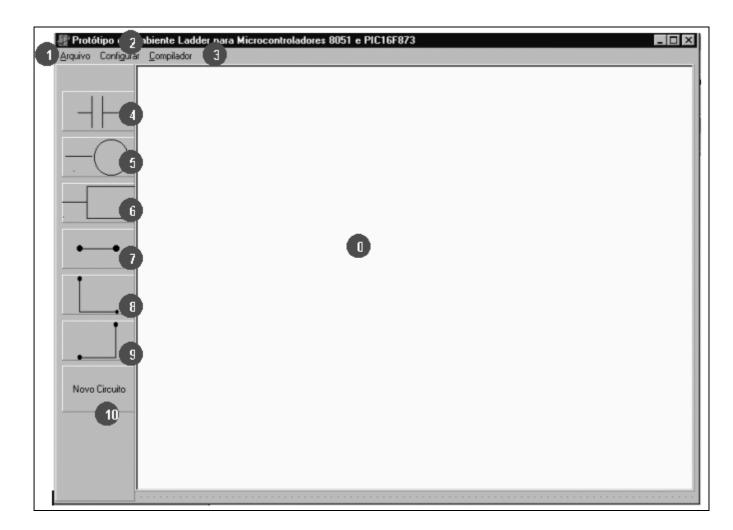

| FIGURA 19 - TELA DE ABERTURA DO PROTÓTIPO                   | 56 |

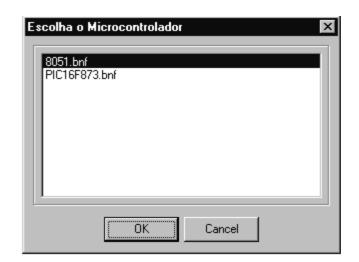

| FIGURA 20 - TELA DE ESCOLHA DO MICROCONTROLADOR             | 57 |

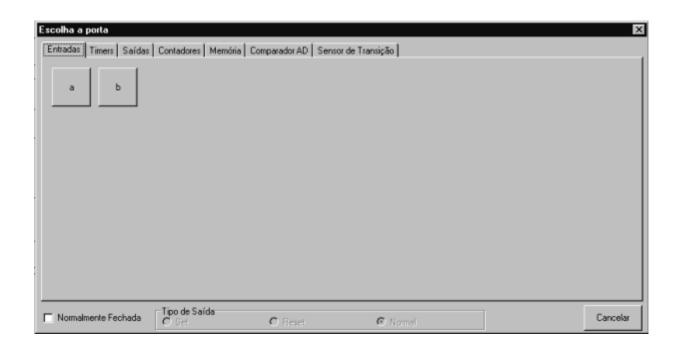

| FIGURA 21 - CONFIGURAÇÃO DE PORTAS                          | 58 |

| FIGURA 22 - ESCOLHENDO A VARIÁVEL                           | 59 |

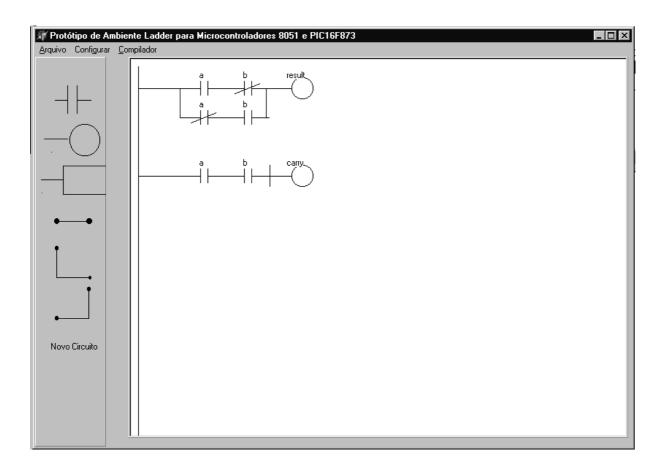

| FIGURA 23 - DIAGRAMA LADDER DE UM MEIO-SOMADOR              | 60 |

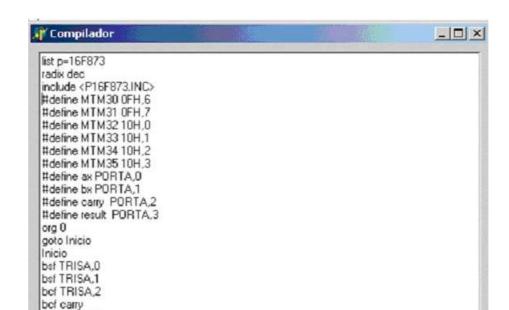

| FIGURA 24 - CÓDIGO ASSEMBLY GERADO DO MEIO SOMADOR          | 61 |

| FIGURA 25 PESULTADO DA MONTAGEM                             | 62 |

### **LISTA DE TABELAS**

| TABELA 1 - PROPRIEDADES DO PIC16F873                                   | 20 |

|------------------------------------------------------------------------|----|

| TABELA 2 - PINAGEM DO PIC16F873                                        | 21 |

| TABELA 3 - REGISTRADORES DE FUNÇÃO ESPECIAL                            | 24 |

| TABELA 4 -REGISTRADORES ENVOLVIDOS NA CONFIGURAÇÃO DA PORTA            | 25 |

| TABELA 5 -REGISTRADORES ENVOLVIDOS NA CONFIGURAÇÃO DA PORTB            | 26 |

| TABELA 6 - REGISTRADORES ENVOLVIDOS NA CONFIGURAÇÃO DA PORTC           | 26 |

| TABELA 7 - REGISTRADOR OPTION_REG                                      | 27 |

| TABELA 8 – CONFIGURAÇÃO DA ORIGEM DO CLOCK                             | 27 |

| TABELA 9 – CONFIGURAÇÃO DO PRESCALER DO TMR0                           | 28 |

| TABELA 10 -REGISTRADOR T1CON                                           | 28 |

| TABELA 11 – CONFIGURAÇÃO DA ORIGEM DO CLOCK DO TMR1                    | 29 |

| TABELA 12 – CONFIGURAÇÃO DO PRESCALER DO TMR1                          | 29 |

| TABELA 13 - REGISTRADORES PARA OPERAÇÃO DE CAPTURA A/D                 | 31 |

| TABELA 14 - REGISTRADOR DE STATUS                                      | 31 |

| TABELA 15 – CONFIGURAÇÃO DOS BANCOS DE MEMÓRIA                         | 31 |

| TABELA 16 - REGISTRADORES DE FUNÇÃO ESPECIAL DO 8051                   | 36 |

| TABELA 17 - REGISTRADORES USADOS NA CONFIGURAÇÃO DO TEMPORIZADORES     |    |

| TABELA 18 – CONFIGURAÇÃO DOS TEMPORIZADORES                            | 37 |

| TABELA 19 – ESQUEMA DE TRADUÇÃO PARA UMA LINGUAGEM DE TRI<br>OPERANDOS |    |

| TABELA 20 – ESQUEMA DE TRADUÇÃO PARA O PIC16F873                       | 54 |

| TABELA 21 – ESQUEMA DE TRADUÇÃO PARA O 8051                            | 55 |

### **SUMÁRIO**

| RESUMO                                   | III |

|------------------------------------------|-----|

| ABSTRACT                                 | IV  |

| LISTA DE FIGURAS                         | V   |

| LISTA DE TABELAS                         | VI  |

| 1 INTRODUÇÃO                             | 10  |

| 1.1 OBJETIVOS DO TRABALHO                | 11  |

| 1.2 ESTRUTURA DO TRABALHO                | 12  |

| 2 LINGUAGEM DIAGRAMA LADDER (LD )        | 13  |

| 2.1 LINHAS DE FORÇA                      | 13  |

| 2.2 ELEMENTOS DE CONEXÃO E ESTADOS       | 13  |

| 2.3 CONTATOS                             | 14  |

| 2.3.1 CONTATOS ESTÁTICOS                 | 15  |

| 2.3.2 CONTATOS SENSORES DE TRANSIÇÃO     | 15  |

| 2.4 BOBINAS                              | 15  |

| 2.4.1 BOBINAS MOMENTÂNEAS                | 16  |

| 2.4.2 BOBINAS <i>LATCH</i>               | 16  |

| 2.4.3 BOBINAS RETENTIVAS                 | 16  |

| 2.4.4 BOBINAS SENSORES DE TRANSIÇÃO      | 17  |

| 2.5 FUNÇÕES E BLOCO DE FUNÇÕES           | 17  |

| 2.5.1 FUNÇÕES DE TEMPORIZADORES          | 17  |

| 2.5.2 FUNÇÕES DE CONTADORES              | 18  |

| 2.5.3 FUNÇÃO CONVERSOR ANALÓGICO/DIGITAL | 18  |

| 2.6 ORDEM DE AVALIAÇÃO DO DIAGRAMA       | 19  |

| 3 MICROCONTROLADORES                          | 20 |

|-----------------------------------------------|----|

| 3.1 MICROCONTROLADOR PIC16F873                | 20 |

| 3.1.1 SPECIAL FUNCTION REGISTERS – SFR        | 23 |

| 3.1.2 CONJUNTO DE INSTRUÇÕES                  | 24 |

| 3.1.3 PORTAS DE ENTRADA/SAÍDA                 | 25 |

| 3.1.3.1 Registrador PORTA                     | 25 |

| 3.1.3.2 Registrador PORTB                     | 25 |

| 3.1.3.3 Utilizando a PORTC                    | 26 |

| 3.1.4 TEMPORIZADORES                          | 27 |

| 3.1.4.1 Temporizador TMR0                     | 27 |

| 3.1.4.2 Temporizador TMR1                     | 28 |

| 3.1.5 CONVERSOR ANALÓGICO/DIGITAL (A/D)       | 29 |

| 3.1.6 UTILIZANDO A MEMÓRIA                    | 31 |

| 3.2 MICROCONTROLADOR 8051                     | 34 |

| 3.2.1 SFR'S (REGISTRADORES ESPECIAIS)         | 35 |

| 3.2.2 PORTAS DE ENTRADA E SAÍDA               | 36 |

| 3.2.3 TEMPORIZADORES                          | 36 |

| 3.2.4 UTILIZANDO MEMÓRIA                      | 37 |

| 4 COMPILADORES                                | 39 |

| 4.1 MODELO DE COMPILAÇÃO DE ANÁLISE E SÍNTESE | 39 |

| 4.2 BNF OU GRAMÁTICA LIVRE DE CONTEXTO        | 40 |

| 4.3 TRADUÇÃO DIRIGIDA PELA SINTAXE            | 41 |

| 4.4 GRAMÁTICA PARA EXPRESSÕES LÓGICAS         | 42 |

| 5 MPLAB                                       | 44 |

| 6 DESENVOLVIMENTO DO TRABALHO                 | 46 |

| 6.1 ESPECIFICAÇÃO                              | 46 |

|------------------------------------------------|----|

| 6.2 ESQUEMAS DE TRADUÇÕES                      | 54 |

| 6.3 OPERACIONALIDADE DA IMPLEMENTAÇÃO          | 55 |

| 6.3.1 PRINCIPAIS FUNÇÕES                       | 55 |

| 6.3.2 INICIANDO UM NOVO PROJETO                | 57 |

| 6.3.3 CONFIGURANDO AS VARIÁVEIS                | 57 |

| 6.3.4 DESENHANDO O DIAGRAMA                    | 59 |

| 6.3.5 COMPILANDO O DIAGRAMA                    | 59 |

| 6.3.6 MONTANDO O CÓDIGO GERADO                 | 61 |

| 7 CONCLUSÕES                                   | 63 |

| 7.1 EXTENSÕES                                  | 63 |

| REFERÊNCIAS BIBLIOGRÁFICAS                     | 64 |

| ANEXO 1 – CONJUNTO DE INSTRUÇÕES DO PIC16F873  | 65 |

| ANEXO 2 – CONJUNTO DE INSTRUÇÕES DO 8051       | 66 |

| ANEXO 3 – ARQUIVO DE CONFIGURAÇÃO DO PIC16F873 | 69 |

| ANEXO 4 – ARQUIVO DE CONFIGURAÇÃO DO 8051      | 74 |

|                                                |    |

### 1 INTRODUÇÃO

Grandes empresas que desenvolvem circuitos integrados estão freqüentemente lançando no mercado novos microcontroladores com recursos computacionais já inclusos no encapsulamento mais conhecidos como *embedded* (programas embutidos).

Todo microcontrolador dispõe de uma linguagem de programação para que se possa programá-lo. Esta linguagem é o *assembly*, linguagem em que a abstração dos dados é muito menor do que aquela apresentada nas linguagens de alto nível.

Há um grande interesse, por parte dos alunos da computação em aprender sobre programação de microcontroladores, mas a grande barreira está na complexidade da programação envolvida nos mesmos, muito diferente das linguagens de alto nível.

Outra motivação para este interesse, é que os microcontroladores têm muitas características em comum com um *personal computer* (PC), como por exemplo, portas seriais, portas paralelas etc; além de serem compactos, discretos e de baixo custo.

Apesar de existirem ferramentas que possibilitam a utilização de linguagens conhecidas como C, Pascal ou Basic, o preço destas ferramentas está além das possibilidades dos alunos.

Uma linguagem de programação genérica para microcontroladores evitaria o esforço de ter que aprender as várias linguagens existentes para cada família destes.

Para tal fim foram criadas linguagens orientadas a programação de microcontroladores.

Uma destas linguagens, conhecida como *Ladder*, é baseada na simbologia gráfica e seus arranjos. Esta linguagem representa o fluxo da corrente elétrica. Possui símbolos que representam contatos (*ON/OFF* - entradas que representam dados do mundo real) e símbolos que representam o comportamento de uma saída quanto à mudança das entradas. Outros símbolos (na forma de retângulos) representam uma macro, ou seja, um conjunto de operações.

Sendo assim, um software capaz de construir e interpretar esta simbologia e convertêla em código *assembly* para o microcontrolador escolhido seria interessante. O contato com a linguagem *Ladder* possibilita também que o aluno familiarize-se com a linguagem muito utilizada usado em controladores lógicos programáveis (CLP's). Este trabalho é uma continuação do trabalho intitulado "Ambiente *Ladder* para o PIC16F874 e 8051" apoiado pelo programa PIPE da Fundação Universidade Regional de Blumenau, realizado no ano de 2000, desenvolvido pelo autor deste trabalho. Entre os resultados obtidos com o referido projeto PIPE, obteve-se uma ferramenta para geração de código *assembly* para o microcontrolador PIC16F84, sem haver a necessidade de conhecimento da linguagem *assembly* do mesmo. Porém, com a inclusão de novos microcontroladores e novas funções, aumenta-se a complexidade do sistema e torna-se necessário rever as técnicas e modelagem empregadas naquele sistema.

Utilizando técnicas de programação existentes para construção de compiladores e modelagem orientada a objetos através da UML, propõe-se refazer o editor que permita representar o diagrama *Ladder*, e a partir deste diagrama a conversão para a linguagem *assembly* específica do respectivo microcontrolador.

### 1.1 OBJETIVOS DO TRABALHO

O objetivo do trabalho é desenvolver uma ferramenta de geração de código *assembly* para os microcontroladores 8051 e PIC16F873, a partir da representação em diagramas *Ladder*.

Os objetivos específicos deste trabalho são:

- a) especificar orientado a objeto, utilizando UML e implementar o código a partir desta especificação;

- b) especificar a linguagem dos microcontroladores usando a forma de Backus-Naur (BNF);

- c) inclusão dos microcontroladores 8051 e PIC16F873 (atualmente só trabalha com o PIC16F84);

- d) inclusão dos blocos de função que permita comparações de sinais analógicos, uso de temporizadores e uso de contadores.

- e) documentar a linguagem Ladder.

### 1.2 ESTRUTURA DO TRABALHO

O primeiro capítulo apresenta os motivos que levaram o autor à realização deste trabalho.

A teoria relativa à linguagem *Ladder* e todos os símbolos utilizados serão apresentados no capítulo 2.

No capítulo 3 será apresentada uma pequena introdução aos microcontroladores. No tópico 3.1 será apresentado o microcontrolador PIC16F873 e suas operações básicas de funcionamento. Apresentará como configurar os elementos necessários ao projeto e apresentará também como está organizada a memória deste componente.

No tópico 3.2 será apresentado o microcontrolador 8051 e suas funcionalidades. Também será apresentada a configuração dos elementos e como está organizada a memória deste componente.

No capítulo 4 será apresentada a teoria básica de compiladores que foi utilizado neste projeto.

Uma breve explicação sobre o montador MPLab será apresentador no capítulo 5.

A especificação, utilizando UML, e a análise de requisitos estarão detalhadas no capítulo 6. Neste capítulo também estará especificada a linguagem dos microcontroladores em BNF.

O funcionamento através de um estudo de caso será apresentado no capítulo 7.

### 2 LINGUAGEM DIAGRAMA LADDER (LD)

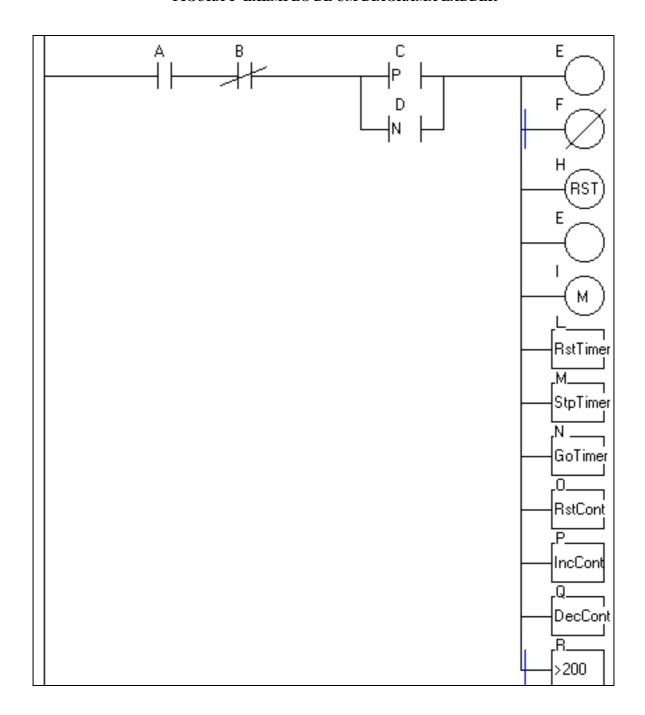

Um programa LD habilita o controlador programável a testar e modificar dados por meio de símbolos gráficos padronizados. Estes símbolos estão dispostos em redes de maneira similar a degraus de uma escada de relés na forma de um diagrama lógico. O diagrama *ladder* é limitado na esquerda e na direita por linhas de força. Na figura 1 um exemplo de um diagrama *ladder*.

### 2.1 LINHAS DE FORÇA

O diagrama *Ladder* deve ser delimitado na esquerda e na direita por linhas verticais chamadas de linha de força da esquerda e de linha de força da direita, respectivamente. A linha de força da direita pode ser explícita ou implícita.

### 2.2 ELEMENTOS DE CONEXÃO E ESTADOS

Como exibidos na figura 1, elementos de conexão podem ser horizontais ou verticais. Os estados dos elementos de conexão devem ser denotados em ligado ou desligado, correspondendo a um valor literal lógico 1 ou 0, respectivamente. O estado da conexão deve ser sinônimo ao termo fluxo de energia.

O estado da linha de força da esquerda deve sempre ser considerado Ligado ou 1. Nenhum estado é definido para a linha da direita.

Um elemento de conexão horizontal deve ser indicado por uma linha horizontal. Um elemento de conexão horizontal transmite o estado do elemento da esquerda imediata para o elemento em sua direita imediata.

Um elemento de conexão vertical deve consistir de uma linha vertical interseccionando-se com uma ou mais conexões horizontais em cada lado. O estado de uma conexão vertical deve representar o OU inclusivo dos estados ligados de uma conexão horizontal em sua esquerda, isto é, o estado de uma conexão vertical deve ser desligado se os estados de todas as conexões horizontais reunidas à esquerda estão desligados; ligado se o estado de uma ou mais das conexões horizontais reunidas à esquerda estão ligadas. Na figura 1, a conexão vertical liga os contatos C e D.

O estado de uma conexão horizontal deve ser copiado para todas as conexões horizontais reunidas a direita.

FIGURA 1 -EXEMPLO DE UM DIAGRAMA LADDER

### 2.3 CONTATOS

Um contato é um elemento que concede um estado a uma conexão horizontal a sua direita que é igual a uma operação lógica E do estado da conexão horizontal ao seu lado esquerdo com uma função apropriada a uma variável lógica associada de entrada, de saída ou

de memória. O contato não modifica o valor da variável lógica associada ao símbolo da esquerda.

### 2.3.1 CONTATOS ESTÁTICOS

Os contatos estáticos se dividem em contatos normalmente abertos e normalmente fechados.

Em um contato normalmente aberto, o estado da conexão da esquerda é copiado para conexão da direita se o estado da variável lógica associado está ligado. Em outros casos o estado da conexão da direita é desligado. Na figura 1, o símbolo A representa um contato normalmente aberto.

Em um contato normalmente fechado, o estado da conexão da esquerda é copiado para a conexão da direita se o estado da variável lógica associado está desligada. Em outros casos o estado da conexão da direita será desligado. Na figura 1, o símbolo B representa um contato normalmente fechado.

### 2.3.2 CONTATOS SENSORES DE TRANSIÇÃO

Os contatos de sensores de transição podem ser classificados em sensores de transição positiva e sensores de transição negativa.

Em um contato sensor de transição positiva, o estado do contato será ligado se for percebida uma transição de desligado para ligado ou de 0 para 1 da avaliação dos símbolos à esquerda deste. O estado do contato será desligado toda as outras vezes. O contato sensor de transição positiva está representado pelo símbolo C na Figura 1.

Em um contato sensor de transição negativa, O estado do contato será ligado ou 1 se for percebida uma transição de ligado para desligado ou de 1 para 0 da avaliação dos símbolos à esquerda deste. O estado do contato será desligado toda as outras vezes. O contato sensor de transição negativa está representado pelo símbolo D na Figura1.

### 2.4 BOBINAS

Uma bobina copia o estado dos contatos a sua esquerda para a conexão a sua direita sem modificação, e armazena uma função apropriada do estado ou transição da conexão da esquerda em uma variável lógica associada.

As bobinas podem ser divididas em momentâneas, latch, sensoras de transição e retentivas.

### 2.4.1 BOBINAS MOMENTÂNEAS

As bobinas momentâneas podem ser classificadas em normal e negada.

Em uma bobina normal, o estado da conexão da esquerda é copiado para a variável lógica associada e para a conexão da direita. Uma bobina está representada na Figura 1, pelo símbolo E.

Em uma bobina negada, o estado da conexão da esquerda é copiado para a conexão da direita. O inverso do estado da conexão da esquerda é copiado para a variável lógica associada, isto é, se o estado da conexão da esquerda for desligado, então o estado da variável associada será ligado e vice-versa. Uma bobina negada está representada na Figura 1, pelo símbolo F.

### 2.4.2 BOBINAS LATCH

As bobinas *latch* podem ser divididas em *set* e *reset*.

Em uma bobina *SET* (*latch*), a variável lógica associada está ativada para o estado ligado quando a conexão da esquerda está ligada, e permanecerá ativada até ser desativada por uma bobina *RESET*. A bobina *SET* está representada no diagrama da Figura 1, pelo símbolo G.

Em uma bobina *RESET* (*unlatch*), A variável lógica associada é desativada para o estado desligado quando a conexão da esquerda está no estado ligado, e permanecerá desativada até ser ativada por uma bobina *SET*. A bobina *RESET* está representada no diagrama da Figura 1, pelo símbolo H.

### 2.4.3 BOBINAS RETENTIVAS

As bobinas retentivas seguem o mesmo comportamento das bobinas normais e bobinas *latch* já descritas anteriormente. A diferença entre as bobinas retentivas e as bobinas normais é que as bobina retentivas representam memórias utilizadas para auxiliar a confecção de programas na linguagem *Ladder*, enquanto o as bobinas normais representam portas de entrada e saída.

Bobinas retentivas têm a mesma representação das bobinas normais, porém dentro do círculo é adicionado um M, conforme representado na Figura 1, pelo símbolo I.

### 2.4.4 BOBINAS SENSORES DE TRANSIÇÃO

As bobinas sensoras de transição podem ser divididas em sensoras de transição positiva e negativa.

Em uma bobina sensora de transição positiva, o estado da variável lógica associada está ligado a partir de uma avaliação deste elemento para o próximo quando a transição da conexão da esquerda for de desligado para ligado, ou de 0 para 1. O estado da bobina será ligado ou 1, quando este evento acontecer. A bobina sensora de transição positiva está representada na Figura 1, pelo símbolo J.

Em uma bobina sensora de transição negativa, o estado da variável lógica associada será ligado a partir de uma avaliação deste elemento para o próximo quando a transição da conexão da esquerda for de ligado para desligado, ou de 1 para 0. O estado da bobina será ligado ou 1, quando este evento acontecer. A bobina sensora de transição negativa está representada na Figura 1, pelo símbolo K.

### 2.5 FUNÇÕES E BLOCO DE FUNÇÕES

A representação de funções e blocos de funções na linguagem Ladder é definida através da figura de um retângulo. Desde que a função possua no mínimo uma entrada e uma saída lógica.

Este projeto utiliza as seguintes funções abaixo.

### 2.5.1 FUNÇÕES DE TEMPORIZADORES

Os temporizadores são previamente configurados em um valor qualquer de tempo, e quando atingem o mesmo, provocam uma mudança de estado lógico no contato correspondente. As seguintes funções são usadas para controlar os temporizadores.

A função reseta *timer* reseta o temporizador, ou seja, reinicia a contagem do tempo a partir do zero. A função está representada no diagrama da Figura 1, pelo símbolo L.

A função pára *timer* interrompe a ação do temporizador mantendo a contagem do tempo até o instante da interrupção. A função está representada no diagrama da Figura 1, pelo símbolo M.

A função avança timer retoma a contagem do temporizador após uma interrupção. A função está representada no diagrama da Figura 1, pelo símbolo N.

### 2.5.2 FUNÇÕES DE CONTADORES

Os contadores, da mesma forma que os temporizadores, são configurados previamente. Quando atingem o valor pré-estabelecido, provocam uma mudança de estado no contato correspondente.

As seguintes funções definem o controle das funções dos contadores.

A função reseta contador reinicia a contagem, zerando a variável associada ao contador. A função está representada no diagrama da Figura 1, pelo símbolo O.

A função incrementa contador adiciona uma unidade ao valor prévio da variável associada ao contador. A função está representada no diagrama da Figura 1, pelo símbolo P.

A função decrementa contador subtrai uma unidade do valor prévio da variável associada ao contador. A função está representada no diagrama da Figura 1, pelo símbolo Q.

### 2.5.3 FUNÇÃO CONVERSOR ANALÓGICO/DIGITAL

A função compara A/D compara o valor obtido da porta conversora de analógico para digital (caso o microcontrolador a possua), com um valor previamente definido. A comparação pode ser maior, menor ou igual ao valor previamente definido.

Quando o valor analógico, comparado ao valor previamente configurado permitir que a expressão lógica configurada seja verdadeira, ativará o *flag* associado ao símbolo. Se for falsa desativará o *flag*.

A função está representada no diagrama da Figura 1, pelo símbolo R.

### 2.6 ORDEM DE AVALIAÇÃO DO DIAGRAMA

A ordem de avaliação dos símbolos do diagrama Ladder é importante para determinar os valores da saídas e ativação das funções. Através desta ordem que se estabelece o fluxo de controle de operações lógicas no diagrama.

A ordem de avaliação dos símbolos do diagrama Ladder é sequencial e deve ser obedecer à ordem do topo para baixo conforme eles aparecem no diagrama. Ou seja avaliam-se primeiros os circuitos mais acima e por último os que estão mais abaixo no diagrama.

### 3 MICROCONTROLADORES

Microcontrolador é um dispositivo que agrega todos os componentes necessários a automação de sistemas como portas de entrada e saída, temporizadores, contadores etc. O microcontrolador corresponde a um microprocessador e seus periféricos típicos, todos juntos num só chip (NICOLOSI, 2001). Microcontrolador (anteriormente chamado de microcomputador de um só *chip*), é um componente que possui todos os periféricos comuns embutidos em uma só pastilha, facilitando assim o desenvolvimento de sistemas pequenos e baratos, embora complexos e sofisticados (SILVA, 1998).

### 3.1 MICROCONTROLADOR PIC16F873

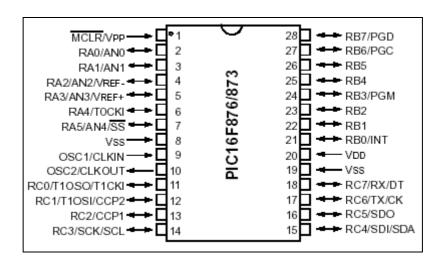

Este microcontrolador fabricado pela Microchip© possui 28 pinos, sendo 22 de portas I/O, foi escolhido por possuir além de todos elementos habituais encontrados nos microcontroladores, como temporizadores, memória, portas de entrada e saída, apresenta conversor de analógico para digital (A/D) de 10 bits. O PIC16F873 possui arquitetura Harvard, onde barramentos de memória e instruções estão separados. Este microcontrolador também possui um reduzido número de instruções para ganhos de performance no processamento de instruções.

Segundo Microchip (2003), o microcontrolador possui as seguintes configurações demonstradas na Tabela 1.

TABELA 1 - PROPRIEDADES DO PIC16F873

| Freqüência de operação                              | DC 20 MHz                |

|-----------------------------------------------------|--------------------------|

| Memória de programa                                 | 4k (palavras de 14 bits) |

| Memória de dados                                    | 192 bytes                |

| Memória de dados EEPROM (eletricamente programável) | 128 bytes                |

| Interrupções                                        | 13                       |

| Portas de entrada e saída                           | Portas A,B, C            |

| Temporizadores                                      | 3                        |

| Modo A/D (analógico para digital) de 10 bits        | 5 canais de entrada      |

| Conjunto de instruções                              | 35                       |

A figura 2, apresenta o microcontrolador e sua pinagem.

FIGURA 2 - PINAGEM DO MICROCONTROLADOR PIC16F873

A tabela 2, descreve detalhadamente as funções dos pinos do PIC16F873.

TABELA 2 - PINAGEM DO PIC16F873

| OSC1/CLKIN       | Entrada para o oscilador de cristal                                                                                    |

|------------------|------------------------------------------------------------------------------------------------------------------------|

| OSC2/CLKOUT      | Saída para o oscilador de cristal                                                                                      |

| MCLR/VPP         | Reinicia o microcontrolador, zerando as mémorias e registradores                                                       |

| RA0/AN0          | Porta de entrada ou saída, pode também ser A/D                                                                         |

| RA1/AN1          | Porta de entrada ou saída, pode também ser A/D                                                                         |

| RA2/AN2/VREF-    | Porta de entrada ou saída, pode também ser A/D, ou tensão de referência negativa.                                      |

| RA3/AN3/VREF+    | Porta de entrada ou saída, pode também ser A/D ou tensão de referência positiva.                                       |

| RA4/T0CKI        | Porta de entrada ou saída, pode também ser entrada para o Timer0                                                       |

| RA5/SS/AN4       | Porta de entrada ou saída, pode também ser A/D                                                                         |

| RB0/INT          | Porta de entrada ou saída, pode ser também pino de interrupção externa.                                                |

| RB1              | Porta de entrada e saída                                                                                               |

| RB2              | Porta de entrada e saída                                                                                               |

| RB3/PGM          | Porta de entrada e saída, pode ser também a entrada de baixa voltagem programada                                       |

| RB4              | Porta de entrada e saída, pode ser também sensor de transição                                                          |

| RB5              | Porta de entrada e saída, pode ser também sensor de transição                                                          |

| RB6/PGC          | Porta de entrada e saída, pode ser também sensor de transição.                                                         |

| RB7/PGD          | Porta de entrada e saída, pode ser também sensor de transição                                                          |

| RC0/T1OSO/T1CKIO | Porta de entrada e saída, pode ser a saída para o oscilador do Timer1 ou <i>clock</i> de entrada para o <i>Timer</i> 1 |

### CONTINUAÇÃO DA TABELA 2

| Porta de entrada ou saída, pode ser a saída para o oscilador do Timer1 ou <i>clock</i> de entrada para o <i>Timer1</i> ou <i>Capture2</i> entrada/ <i>Compare2</i> saída/PWM2 saída. |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Porta de entrada ou saída, pode ser também <i>Capture1</i> entrada/ <i>Compare1</i> saída/PWM1 saída.                                                                                |

| Porta de entrada ou saída, pode ser também o <i>clock</i> serial síncrono entrada/saída para ambos SPI e I2C modos                                                                   |

| Porta de entrada ou saída, pode ser também SPI <i>Data In</i> (SPI modo) ou dados I/O (I2C modo).                                                                                    |

| Porta de entrada ou saída, pode ser também SPI Data Out (SPI modo).                                                                                                                  |

| Porta de entrada ou saída, pode ser também a USART transmissor assíncrono ou <i>clock</i> síncrono.                                                                                  |

| Porta de entrada ou saída, pode ser também a USART receptor assíncrono ou dados síncronos.                                                                                           |

| Referência de terra para lógica e pinos I/O                                                                                                                                          |

| Referência positiva para lógica e pinos I/O.                                                                                                                                         |

|                                                                                                                                                                                      |

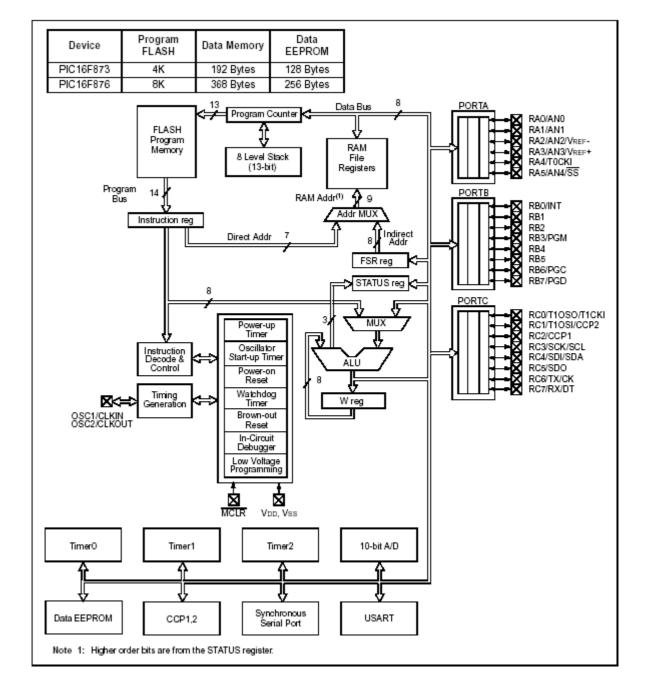

É um microcontrolador de arquitetura Harvard, que prevê várias vias de comunicação entre CPU e periféricos, permitindo a realização de várias operações simultaneamente, o que implica em aumento considerável na velocidade de execução e permite ainda que as memórias de dados e a de programa tenham tamanhos diferentes (SILVA, 1998).

A arquitetura deste microcontrolador está ilustrada na Figura 3.

FIGURA 3 -DIAGRAMA DA ARQUITETURA INTERNA DO PIC16F873

### 3.1.1 SPECIAL FUNCTION REGISTERS – SFR

Os SFR's (registradores de funções especiais) são muito utilizados na configuração dos elementos que compõem o microcontrolador. Servem para configurar portas, ativar interrupções e outras funções. Segundo Microchip, 2003 os mais usados registradores de funções especiais do PIC16F873 são os seguintes representados na Tabela 3.

TABELA 3 - REGISTRADORES DE FUNÇÃO ESPECIAL

| Endereço | Registrador | Função                                              |

|----------|-------------|-----------------------------------------------------|

| Bank0    |             | •                                                   |

| 01h      | TMR0        | Módulo do <i>Timer0</i>                             |

| 05h      | PORTA       | Registrador de estado da Porta A                    |

| 06h      | PORTB       | Registrador de estado da Porta B                    |

| 07h      | PORTC       | Registrador de estado da Porta C                    |

| 0Eh      | TMR1L       | Módulo dos bits menos significativos do Timer1      |

| 0Fh      | TMR1H       | Módulo dos bits mais significativos do Timer1       |

| 10h      | T1CON       | Controle do Timer1                                  |

| 1Eh      | ADRESH      | Módulo dos bits mais significativos da captura A/D  |

| 1Fh      | ADCON0      | Controle da captura A/D                             |

| Bank1    |             |                                                     |

| 81h      | OPTION_REG  | Configuração do registrador Timer0                  |

| 85h      | TRISA       | Configuração do modo de operação da Porta A         |

| 86h      | TRISB       | Configuração do modo de operação da Porta B         |

| 87h      | TRISC       | Configuração do modo de operação da Porta C         |

| 8Bh      | INTCON      | Controle de interrupções                            |

| 9Eh      | ADRESL      | Módulo dos bits menos significativos da captura A/D |

| 9Fh      | ADCON1      | Controle da captura A/D                             |

Estes registradores serão explicados de forma mais detalhada nos items a seguir.

### 3.1.2 CONJUNTO DE INSTRUÇÕES

O PIC está encaixado na categoria RISC (conjunto de instruções reduzido), por possuir apenas 35 instruções que atendem ao funcionamento básico de um sistema microcontrolado. Como os barramentos de memória e de programa estão separados o tamanho da palavra de memória das instruções não precisa ter o mesmo tamanho da memória de dados. No PIC o tamanho do código de operação é de 14 bits. Isto permite que instruções que levariam 2 passos ou mais sejam executados em uma só passagem.

No anexo 1 estão relacionadas as instruções do microcontrolador PIC16F873.

### 3.1.3 PORTAS DE ENTRADA/SAÍDA

As portas são o elo de ligação do microcontrolador com o mundo exterior. Através delas que se realizam todas as comunicações com os periféricos. O PIC16F873 possui 22 portas com diversas funcionalidades.

Estas funcionalidades serão apresentadas a seguir.

### 3.1.3.1 REGISTRADOR PORTA

Segundo Microchip (2003), PORTA é uma porta bidirecional (entrada ou saída) de 6-bit de largura. O registrador correspondente a configuração da direção dos dados (saída ou entrada) é o registrador TRISA. Configurando o bit TRISA igual a 1 torna o correspondente bit do registrador PORTA uma entrada e configurando como 0 uma saída.

Os pinos de PORTA também são multiplexados com entradas analógicas. A operação de cada pino é selecionada pela configuração dos bits de controle do registrador ADCON1. O usuário também deve assegurar que o bit correspondente no registrador TRISA da porta usada esteja configurado em 1 quando usar entradas analógicas.

A Tabela 4 apresenta os registradores usados para configuração da PORTA e seus respectivos pinos.

TABELA 4 -REGISTRADORES ENVOLVIDOS NA CONFIGURAÇÃO DA PORTA

| Endereço | Nome   | Bit 7                                    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| 05h      | PORTA  |                                          |       | RA5   | RA4   | RA3   | RA2   | RA1   | RA0   |

| 85h      | TRISA  | Registrador de direção de dados da PORTA |       |       |       |       |       |       |       |

| 9Fh      | ADCON1 |                                          |       |       |       | PCFG3 | PCFG2 | PCFG1 | PCFG0 |

### 3.1.3.2 REGISTRADOR PORTB

Segundo Microchip (2003), PORTB é uma porta bidirecional de 8-bits de largura. O registrador correspondente a configuração da direção dos dados (saída ou entrada) é o

registrador TRISB. Configurando o bit TRISB igual a 1 torna o correspondente bit do registrador PORTB uma entrada e configurando como 0 uma saída.

Os pinos de PORTB podem ser programados sensores de transição. Para tal operação os pinos do TRISB devem estar configurados como entradas. O pino RBIF do registrador INTCON também deve estar configurado em 0.

A Tabela 5 apresenta os registradores usados para configuração da PORTA e seus respectivos pinos.

TABELA 5 -REGISTRADORES ENVOLVIDOS NA CONFIGURAÇÃO DA PORTB

| Endereço  | Nome   | Bit 7                                    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----------|--------|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| 06h, 106h | PORTB  | RB7                                      | RB6   | RB5   | RB4   | RB3   | RB2   | RB1   | RB0   |

| 86h, 186h | TRISB  | Registrador de direção de dados da PORTB |       |       |       |       |       |       |       |

| 8Bh       | INTCON |                                          |       |       |       |       |       |       | RBIF  |

### 3.1.3.3 UTILIZANDO A PORTC

Segundo Microchip (2003), PORTC é uma porta bidirecional de 8-bits de largura. O registrador correspondente à configuração da direção dos dados (saída ou entrada) é o registrador TRISC. Configurando o bit TRISC igual a 1 torna o correspondente bit do registrador PORTC uma entrada e configurando como 0 uma saída.

A Tabela 6 apresenta os registradores usados para configuração da PORTA e seus respectivos pinos.

TABELA 6 - REGISTRADORES ENVOLVIDOS NA CONFIGURAÇÃO DA PORTB

| Endereço | Nome  | Bit 7                                    | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|-------|------------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| 07h      | PORTC | RC7                                      | RC6   | RC5   | RC4   | RC3   | RC2   | RC1   | RC0   |

| 87h      | TRISC | Registrador de direção de dados da PORTC |       |       |       |       |       |       |       |

### 3.1.4 TEMPORIZADORES

Os temporizadores são utilizados quando se deseja ter controle sobre o tempo de alguma determinada tarefa. O PIC16F873 possui 3 temporizadores TMR0 (Timer 0), TMR1 (Timer 1) e TMR2 (Timer 2). Os temporizadores do PIC16F873 podem ser configurados por clock interno ou externo, exceto o TMR2, que só pode ser configurado como externo.

O funcionamento e os registradores envolvidos na configuração deste registradores serão detalhado a seguir.

### 3.1.4.1 TEMPORIZADOR TMR0

O TMR0 ou temporizador 0 é um registrador de 8 bits que é incrementado automaticamente conforme as configurações dos registradores relacionados. Este registrador trabalha com a freqüência do oscilador, ou seja, 20 MHz. Este temporizador não tem controle de avanço e parada.

Para selecionar a origem do clock este recurso é necessário configurar o registrador OPTION\_REG (registrador de opções). Este registrador permite configurar o comportamento do TMRO. A tabela 7 apresenta este registrador e os bits envolvidos na configuração do TMRO. A tabela 8 demonstra como configurar a origem do clock e o para quem se destina o prescaler através dos bits de controle.

TABELA 7 - REGISTRADOR OPTION REG

| Endereço | Nome       | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 81H      | OPTION_REG |       |       | TOCS  | TOSE  | PSA   | PS2   | PS1   | PS0   |

TABELA 8 - CONFIGURAÇÃO DA ORIGEM DO CLOCK

| bit 5 T0CS(Timer 0 clock source) TMR0 seletor da origem do Clock bit |                                               |  |  |  |  |

|----------------------------------------------------------------------|-----------------------------------------------|--|--|--|--|

| 1                                                                    | Transição no pino T0CKI                       |  |  |  |  |

| 0                                                                    | Clock Interno                                 |  |  |  |  |

| bit 3 PSA (Prescaler assignment) Configuração                        | do Prescaler                                  |  |  |  |  |

| 1                                                                    | Prescaler é atribuído ao WDT (watchdog timer) |  |  |  |  |

| 0                                                                    | Prescaler é atribuído ao módulo do Timer0     |  |  |  |  |

Este temporizador possui configuração de escala através dos bits 0 ao bit 4 do registrador OPTION\_REG. A escala serve para determinar tempos curtos ou tempos longos. A tabela 9 demonstra quais são os bits e as opções de escalas relacionadas para o registrador TMR0 e como configurá-las.

TABELA 9 - CONFIGURAÇÃO DO PRESCALER DO TMRO

|     | Bit |     | bits de seleção do fator do Prescaler                      |

|-----|-----|-----|------------------------------------------------------------|

| PS2 | PS1 | PS0 |                                                            |

| 0   | 0   | 0   | 1:2 (incrementa Timer0 a cada dois ciclos do clock)        |

| 0   | 0   | 1   | 1:4 (incrementa Timer0 a cada 4 ciclos do <i>clock</i> )   |

| 0   | 1   | 0   | 1:8 (incrementa Timer0 a cada 8 ciclos do <i>clock</i> )   |

| 0   | 1   | 1   | 1:16 (incrementa Timer0 a cada 16 ciclos do <i>clock</i> ) |

| 1   | 0   | 0   | 1:32 (incrementa Timer0 a cada 32 ciclos do <i>clock</i> ) |

| 1   | 0   | 1   | 1:64 (incrementa Timer0 a cada 64 ciclos do <i>clock</i> ) |

| 1   | 1   | 0   | 1:128 (incrementa Timer0 a cada 128 ciclos do clock)       |

| 1   | 1   | 1   | 1:256 (incrementa Timer0 a cada 256 ciclos do clock)       |

### 3.1.4.2 TEMPORIZADOR TMR1

O TMR1L e o TMR1H juntos formam um registrador de 16 bits para temporizador 1 que é incrementado automaticamente conforme as configurações dos registradores relacionados. Este registrador trabalha com a freqüência do oscilador dividida por 4, ou seja para um *clock* de 20MHZ sua freqüência será de 5 MHZ.

O comportamento do temporizador TMR1 é determinador pelo T1CON (Controle do do Timer1). O registrador T1CON e seus bits de controle estão demonstrados na tabela 10.

TABELA 10 -REGISTRADOR T1CON

| Endereço | Nome  | Bit 7 | Bit 6 | Bit 5   | Bit 4   | Bit 3 | Bit 2 | Bit 1  | Bit 0  |

|----------|-------|-------|-------|---------|---------|-------|-------|--------|--------|

| 10H      | T1CON |       |       | T1CKPS1 | T1CKPS0 |       |       | TMR1CS | TMR10N |

Para configurar a origem do clock do TMR1 deve-se configurar o bit TMR1CS (origem do clock do Timer1) conforme demonstrado na tabela 11.

TABELA 11 - CONFIGURAÇÃO DA ORIGEM DO CLOCK DO TMR1

| bit 1 | TMR1CS: bit de seleção da origem do clock do Timer1 |

|-------|-----------------------------------------------------|

| 1     | Clock externo do pino RC0/T1OSO/T1CKI               |

| 0     | Clock Interno (Freqüência do oscilador/4)           |

Este temporizador também possui controle de escala que são determinados pelos bits 5 e 4 do registrador T1CON. As opções de escalas estão apresentadas na tabela 12.

TABELA 12 -CONFIGURAÇÃO DO PRESCALER DO TMR1

| T1CKPS1 | T1CKPS0 | bits de seleção d | bits de seleção do prescaler do Timer1                |  |  |  |  |  |  |

|---------|---------|-------------------|-------------------------------------------------------|--|--|--|--|--|--|

| 1       | 1       | 1:8               | incremento dos registradores a cada 8 ciclos do clock |  |  |  |  |  |  |

| 1       | 0       | 1:4               | incremento dos registradores a cada 4 ciclos do clock |  |  |  |  |  |  |

| 0       | 1       | 1:2               | incremento dos registradores a cada 2 ciclos do clock |  |  |  |  |  |  |

| 0       | 0       | 1:1               | incremento dos registradores a cada 1 ciclo do clock  |  |  |  |  |  |  |

O TMR1 diferente do TMR0, possui controle de parada do temporizador. Este controle é feito através do bit 0 do registrador T1CON. Se estiver em 1 o temporizador está ativo e se estiver em 0 o temporizador para a contagem.

Para testar se o tempo do Timer1 acabou ou não, checa-se o bit TMR1IF do registrador PIR1 está ligado. Se estiver em 1 terminou o tempo.

### 3.1.5 CONVERSOR ANALÓGICO/DIGITAL (A/D)

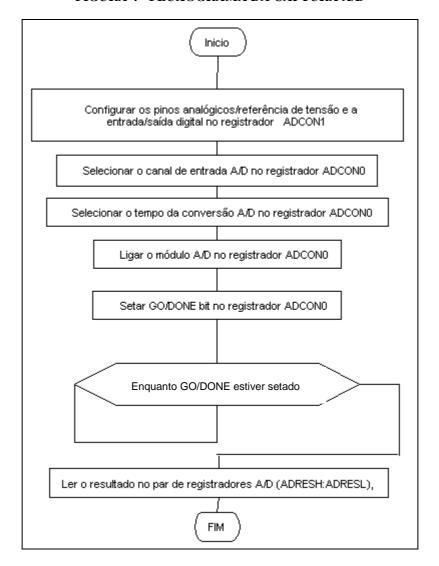

Segundo Microchip (2003), para configurar a leitura da porta A/D deve-se seguir os seguintes passos, conforme o fluxograma da figura.

FIGURA 4 - FLUXOGRAMA DA CAPTURA A/D

Na tabela 13 estão representados os registradores usados nesta operação e seus respectivos bits de controle.

TABELA 13 - REGISTRADORES PARA OPERAÇÃO DE CAPTURA A/D

| Endereço | Nome   | Bit 7                                     | Bit 6      | Bit 5     | Bit 4     | Bit 3   | Bit 2   | Bit 1 | Bit 0 |

|----------|--------|-------------------------------------------|------------|-----------|-----------|---------|---------|-------|-------|

| 1FH      | ADCON1 | ADCS1                                     | ADCS2      | CHS2      | CHS1      | CHS0    | GO/DONE |       | ADON  |

| 9FH      | ADCON2 | ADFM                                      |            |           |           | PCF3    | PCFG2   | PCFG1 | PCFG0 |

| 1EH      | ADRESH | Bits mais significativos da conversão A/D |            |           |           |         |         |       |       |

| 9EH      | ADRESL | Bits men                                  | os signifi | cativos d | a convers | são A/D |         |       |       |

| ОСН      | PIR    |                                           | ADIF       |           |           |         |         |       |       |

| 8CH      | PIE    |                                           | ADIE       |           |           |         |         |       |       |

| 8BH      | INTCON | GIE                                       | PEIE       |           |           |         |         |       |       |

### 3.1.6 UTILIZANDO A MEMÓRIA

O PIC possui quatro bancos de memória endereçáveis configurados através dos pinos RP1 e RP0 do registrador STATUS representado na tabela 14. Para mudar de banco de memória precisa-se configurar os pinos RP1 e RP0 do registrador de STATUS conforme demonstrado na tabela 15.

TABELA 14 - REGISTRADOR DE STATUS

| Endereço | Nome   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 03H      | STATUS |       | RP1   | RP0   |       |       |       |       |       |

TABELA 15 -CONFIGURAÇÃO DOS BANCOS DE MEMÓRIA

| Bits |     |                  |

|------|-----|------------------|

| RP1  | RP0 | Banco de memória |

| 0    | 0   | 0                |

| 0    | 1   | 1                |

| 1    | 0   | 2                |

| 1    | 1   | 3                |

No banco 1 de memória a partir do endereço 20H é possível obter 96 bytes de RAM e no banco 0 de memória a partir do endereço A0H mais 96 bytes.

A figura 5, extraída de Microchip (2003), demonstra como está organizada a memória do PIC16F873 e quais memórias estão reservadas para registradores e quais estão disponíveis para o uso.

FIGURA 5 - MAPA DA MEMÓRIA DO PIC16F873

|                      | File<br>Address                                                                                                                                                                                                | Į.                   | File<br>Address |                   | File<br>Address |                         | File<br>Address |

|----------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-----------------|-------------------|-----------------|-------------------------|-----------------|

| Indirect addr. (*)   | 00h                                                                                                                                                                                                            | Indirect addr.(*)    | 80h             | Indirect addr.(*) | 100h            | Indirect addr. (*)      | 180h            |

| TMR0                 | 01h                                                                                                                                                                                                            | OPTION_REG           | 81h             | TMR0              | 101h            | OPTION REG              | 181h            |

| PCL                  | 02h                                                                                                                                                                                                            | PCL                  | 82h             | PCL               | 102h            | PCL                     | 182h            |

| STATUS               | 03h                                                                                                                                                                                                            | STATUS               | 83h             | STATUS            | 103h            | STATUS                  | 183h            |

| FSR                  | 04h                                                                                                                                                                                                            | FSR                  | 84h             | FSR               | 104h            | FSR                     | 184h            |

| PORTA                | 05h                                                                                                                                                                                                            | TRISA                | 85h             |                   | 105h            |                         | 185h            |

| PORTB                | 06h                                                                                                                                                                                                            | TRISB                | 86h             | PORTB             | 106h            | TRISB                   | 186h            |

| PORTC                | 07h                                                                                                                                                                                                            | TRISC                | 87h             |                   | 107h            |                         | 187h            |

| PORTD <sup>(1)</sup> | 08h                                                                                                                                                                                                            | TRISD <sup>(1)</sup> | 88h             |                   | 108h            |                         | 188h            |

| PORTE <sup>(1)</sup> | 09h                                                                                                                                                                                                            | TRISE <sup>(1)</sup> | 89h             |                   | 109h            |                         | 189h            |

| PCLATH               | 0Ah                                                                                                                                                                                                            | PCLATH               | 8Ah             | PCLATH            | 10Ah            | PCLATH                  | 18Ah            |

| INTCON               | 0Bh                                                                                                                                                                                                            | INTCON               | 8Bh             | INTCON            | 10Bh            | INTCON                  | 18Bh            |

| PIR1                 | 0Ch                                                                                                                                                                                                            | PIE1                 | 8Ch             | EEDATA            | 10Ch            | EECON1                  | 18Ch            |

| PIR2                 | 0Dh                                                                                                                                                                                                            | PIE2                 | 8Dh             | EEADR             | 10Dh            | EECON2                  | 18Dh            |

| TMR1L                | 0Eh                                                                                                                                                                                                            | PCON                 | 8Eh             | EEDATH            | 10Eh            | Reserved <sup>(2)</sup> | 18Eh            |

| TMR1H                | 0Fh                                                                                                                                                                                                            | . 33.1               | 8Fh             | EEADRH            | 10Fh            | Reserved <sup>(2)</sup> | 18Fh            |

| T1CON                | 10h                                                                                                                                                                                                            |                      | 90h             |                   | 110h            |                         | 190h            |

| TMR2                 | 11h                                                                                                                                                                                                            | SSPCON2              | 91h             |                   |                 |                         |                 |

| T2CON                | 12h                                                                                                                                                                                                            | PR2                  | 92h             |                   |                 |                         |                 |

| SSPBUF               | 13h                                                                                                                                                                                                            | SSPADD               | 93h             |                   |                 |                         |                 |

| SSPCON               | 14h                                                                                                                                                                                                            | SSPSTAT              | 94h             |                   |                 |                         |                 |

| CCPR1L               | 15h                                                                                                                                                                                                            |                      | 95h             |                   |                 |                         |                 |

| CCPR1H               | 16h                                                                                                                                                                                                            |                      | 96h             |                   |                 |                         |                 |

| CCP1CON              | 17h                                                                                                                                                                                                            |                      | 97h             |                   |                 |                         |                 |

| RCSTA                | 18h                                                                                                                                                                                                            | TXSTA                | 98h             |                   |                 |                         |                 |

| TXREG                | 19h                                                                                                                                                                                                            | SPBRG                | 99h             |                   |                 |                         |                 |

| RCREG                | 1Ah                                                                                                                                                                                                            |                      | 9Ah             |                   |                 |                         |                 |

| CCPR2L               | 1Bh                                                                                                                                                                                                            |                      | 9Bh             |                   |                 |                         |                 |

| CCPR2H               | 1Ch                                                                                                                                                                                                            |                      | 9Ch             |                   |                 |                         |                 |

| CCP2CON              | 1Dh                                                                                                                                                                                                            |                      | 9Dh             |                   |                 |                         |                 |

| ADRESH               | 1Eh                                                                                                                                                                                                            | ADRESL               | 9Eh             |                   |                 |                         |                 |

| ADCON0               | 1Fh                                                                                                                                                                                                            | ADCON1               | 9Fh             |                   | 4006            |                         | 1406            |

|                      | 20h                                                                                                                                                                                                            |                      | A0h             |                   | 120h            |                         | 1A0h            |

| General              |                                                                                                                                                                                                                | General              |                 |                   |                 |                         |                 |

| Purpose              |                                                                                                                                                                                                                | Purpose              |                 | accesses          |                 | accesses                |                 |

| Register             |                                                                                                                                                                                                                | Register             |                 | 20h-7Fh           |                 | A0h - FFh               |                 |

| 96 Bytes             |                                                                                                                                                                                                                | 96 Bytes             |                 |                   | 16Fh<br>170h    |                         | 1EFh<br>1F0h    |

|                      | 75.                                                                                                                                                                                                            |                      | FF.             |                   |                 |                         |                 |

| Bank 0               | J 7Fh                                                                                                                                                                                                          | Bank 1               | FFh             | Bank 2            | 17Fh            | Bank 3                  | 1FFh            |

| * Notal              | Unimplemented data memory locations, read as '0'.  * Not a physical register.  Note 1: These registers are not implemented on the PIC16F873.  2: These registers are reserved, maintain these registers clear. |                      |                 |                   |                 |                         |                 |

### 3.2 MICROCONTROLADOR 8051

Segundo Lima (2003), o microcontrolador 8051, da Intel, é, sem dúvida, o microcontrolador mais popular atualmente. O dispositivo em si é um microcontrolador de 8 bits relativamente simples, mas com ampla aplicação. O 8051 utiliza tipicamente um clock de 12 MHz, com tempos de execução de cada instrução variando entre 1µs e 4µs.

A figura 6, apresenta a pinagem do 8051

P1.0 🔟 ₩ VCC P1.1 🗵 39 PO.O ADO P1.2 3 38 PO.1 AD1 P1.3 重 <sup>3</sup>रा PO.2 AD2 P1.4 5 36 PO.3 AD3 AD4 P1.5 6 35 PO.4 34 PO.5 AD5 P1.6 📧 P1.7 🔞 33 PO.6 AD6 RST 9 32 PO.7 AD7 31 EA RXD / P3.0 🔟 TXD / P3.1 🔟 30 ALE 5 29 PSEN INTO / P3.2 12 INT1 / P3.3 15 35 P2.7 A15 TO / P3.4 14 ₹ P2.6 A14 T1/P3.5 15 ∞ P2.5 A13 WR / P3.6 16 ፮ P2.4 A12 RD / P3.7 IT 24 P2.3 A11 XTAL1 18 ፮ P2.2 A10 XTAL2 19 22 P2.1 Α9 GND 🔯 21 P2.O A8

FIGURA 6 - PINAGEM DO 8051.

Além do microprocessador, um sistema básico como este tem os seguintes elementos:

a) *Interrupções*: são entradas a partir de um sinal externo que fazem com que o processamento seja interrompido e seja iniciada uma subrotina específica.

- b) Gerador de Reset: responsável por inicializar o sistema ao ligar ou quando acionado.

- c) Gerador de Clock: gera os pulsos necessários ao sincronismo do sistema.

- d) *Memória de Programa*: memória onde o microprocessador vai procurar as instruções a executar. Em sistemas dedicados costuma-se utilizar memórias ROM, embora em alguns casos memórias RAM também sejam utilizadas.

- e) *Memória de Dados*: memória onde o microprocessador lê e escreve dados durante a operação normal. Geralmente é do tipo volátil, embora memórias não-voláteis possam ser utilizadas.

- f) Seleção de Endereços: lógica para escolher qual memória ou periférico o microprocessador vai utilizar.

- g) Portas de I/O: sua função é a comunicação com o mundo externo. Através delas dispositivos como teclados, impressoras, displays, entre outros, comunicam-se com o sistema.

Este microcontrolador possui um complexo número de instruções que estão listadas no anexo 2.

### 3.2.1 SFR'S (REGISTRADORES ESPECIAIS)

Segundo Lima (2003), os Registradores de Função Especial (SFRs - Special Function Registers) são responsáveis pela maior partes do controle do 8051. Os mesmos estão listados na tabela 11, sendo que alguns deles possuem bits endereçáveis. Alguns dos bits endereçáveis possuem inclusive um nome mnemônico, para maior facilidade de desenvolvimento de software em compiladores.

TABELA 16 - REGISTRADORES DE FUNÇÃO ESPECIAL DO 8051

| 80h | P0   | Registrador de estado da P0                            |

|-----|------|--------------------------------------------------------|

| 90h | P1   | Registrador de estado da P1                            |

| A0  | P2   | Registrador de estado da P2                            |

| ВО  | P3   | Registrador de estado da P3                            |

| 88H | TCON | Registro dos Temporizadores/Contadores. Permitem       |

|     |      | a programação dos mesmos.                              |

| 89H | TMOD | Registro dos Temporizadores/Contadores. Permitem       |

|     |      | a programação dos mesmos.                              |

| 8AH | TL0  | Registro de configuração dos bits menos significativos |

|     |      | do T0                                                  |

| 8CH | TH0  | Registro de configuração dos bits mais significativos  |

|     |      | do T0                                                  |

| 8BH | TL1  | Registro de configuração dos bits menos significativos |

|     |      | do T1                                                  |

| 8DH | TH1  | Registro de configuração dos bits mais significativos  |

|     |      | do T1                                                  |

| A8H | IE   | Registro para programação das interrupções             |

| B8H | IP   | Registro para programação das interrupções.            |

| D0H | PSW  | (Program Status Word - palavra de status do            |

| -   |      | programa) é o registro dos Flags do 8051               |

| E0H | ACC  | É o acumulador.                                        |

| F0H | В    | Registro auxiliar B.                                   |

|     |      |                                                        |

A seguir, serão mostrados com mais detalhes de alguns dos registradores de funções especiais.

### 3.2.2 PORTAS DE ENTRADA E SAÍDA

Diferentemente do microcontrolador PIC16F873, as portas do 8051 já são de três estados, ou seja, não há necessidade de configurar nenhum registrador para determinar a direção da porta. Basta executar qualquer leitura ou escrita nos registradores P0, P1, P2, P3.

### 3.2.3 TEMPORIZADORES

Para utilizar os temporizadores é necessários configurar os registradores TCON (registrador de controle) e TMOD (registrador de modo de operação). Conforme a configuração eles se incrementam automaticamente até ocorrer o final do tempo selecionado que é indicado pelo TF1.

A tabela 17 demonstra os bits de configuração os registradores TCON e TMOD e a tabela 18 demonstra como configurá-los.

TABELA 17 - REGISTRADORES USADOS NA CONFIGURAÇÃO DOS TEMPORIZADORES

| Endereço | Nome | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|------|-------|-------|-------|-------|-------|-------|-------|-------|

| 89H      | тмор | GATE  | C/T   | M1    | MO    | GATE  | C/T   | M1    | МО    |

| 88H      | TCON | TF1   | TR1   | TF0   | TR0   |       |       |       |       |

TABELA 18 - CONFIGURAÇÃO DOS TEMPORIZADORES

| Bits                                  |     | Função                              |

|---------------------------------------|-----|-------------------------------------|

| Gate aciona o disparo por interrupção |     | aciona o disparo por interrupção    |

| C                                     | ;/T | modo contador ou temporizador       |

| M1                                    | M0  | Modo de operação                    |

| 0                                     | 0   | Contador de 13 bits                 |

| 0                                     | 1   | Contador de 16 bits                 |

| 1                                     | 0   | Contador de 8 bits com auto-recarga |

| 1                                     | 1   | Timer misto                         |

| Т                                     | F1  | Flag de estouro temporizador 1      |

| Т                                     | R1  | Controle do temporizador 1          |

| TF0 Flag de estouro do temporizador 0 |     |                                     |

| TR0 Controle do temporizador 0        |     |                                     |

# 3.2.4 UTILIZANDO MEMÓRIA

O microcontrolador 8051 possui uma RAM interna de 256 bytes sendo a memória de dados vai de 7FH a 00H ou 128 bytes. O resto da memória está alocado para os registradores de funções especiais.

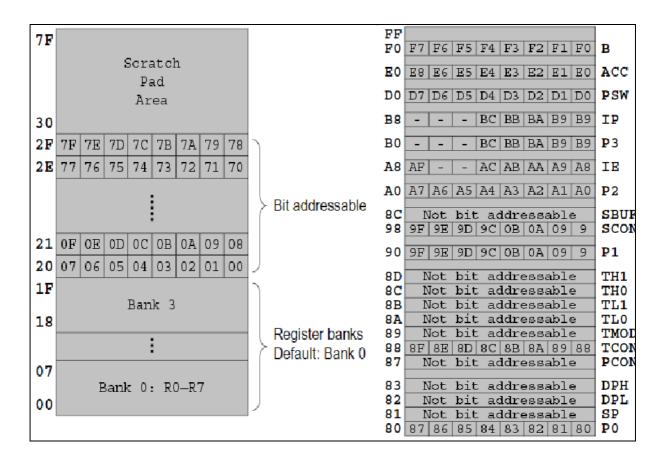

As posições de memória de 20H até 2F são endereçáveis por bit. A figura 7 apresenta o mapa de memória do 8051.

#### FIGURA 7 -MAPA DE MEMÓRIA DO 8051

### **4 COMPILADORES**

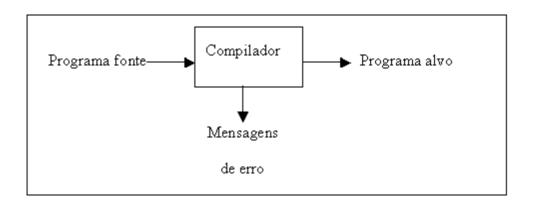

Segundo Aho (1995), um compilador é um programa que lê um programa escrito numa linguagem – a linguagem fonte – e o traduz num programa equivalente em outra linguagem – a linguagem alvo.

Os compiladores são algumas vezes classificados como de uma passagem, de passagens múltiplas, de carregar e executar, depuradores ou otimizantes.

A figura 8 representa um diagrama de um compilador.

FIGURA 8 - DIAGRAMA DE UM COMPILADOR

# 4.1 MODELO DE COMPILAÇÃO DE ANÁLISE E SÍNTESE

Segundo Aho (1995), existem duas partes na compilação: a análise e a síntese. A parte de análise divide o programa em partes constituintes e cria uma representação intermediária do mesmo. A de síntese constrói o programa alvo desejado a partir da representação intermediária.

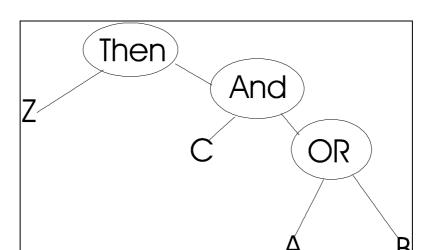

Para exemplificar vamos exemplificar a compilação da seguinte operação lógica IF (A or B) and C then Z. Como a maioria das linguagens assembly trabalha com 2 operandos precisa-se dividir esta instrução de 4 operandos em instruções de 2 operandos.

Como pode ser observar na figura 9 a árvore foi divida em instruções e em operandos, sendo os operandos, folhas da árvore e as instruções, nós da árvore.

FIGURA 9 - ÁRVORE DA OPERAÇÃO IF (A OR B) AND C THEN Z

Já o processo de síntese consiste em transformar esta árvore em programa alvo para a linguagem correspondente. O quadro 1 ilustra a tradução da árvore da figura 8 para uma linguagem alvo de três operandos. Cada nó da árvore torna-se uma variável temporária e a árvore é analisada das folhas até chegar a raiz que representa o resultado da instrução conforme demonstrado no quadro 1.

QUADRO 1 – TRADUÇÃO DA EXPRESSÃO IF (A OR B) AND C THEN Z

Temp1:=A or B

Temp2:=Temp1 and C

Z:=temp2

## 4.2 BNF OU GRAMÁTICA LIVRE DE CONTEXTO

Segundo Aho (1995), uma gramática de livre contexto ou BNF (forma de Backus-Naur) é utilizada para representar a sintaxe de uma linguagem. Além de especificar a sintaxe da linguagem, pode ser usada como auxílio para guiar a tradução do programa.

Uma gramática de livre contexto possui quatro componentes.

- a. Um conjunto de *tokens* (palavras-chaves como *while*, por exemplo), conhecidos como símbolos terminais;

- b. Um conjunto de não-terminais;

- c. Um conjunto de produções, onde uma produção consiste de um nãoterminal, chamado de lado esquerdo da produção, uma seta e uma sequência de *tokens* e/ou não-terminais, chamados de lado direito da produção.

- d. Uma designação a um dos não-terminais como símbolo de partida.

Para melhor entendimento convenciona-se que os símbolos não-terminais serão itálicos, os *tokens* formados por cadeias de caracteres em negrito e os outros tokens, como dígitos e operandos aritméticos e lógicos, sem itálico ou negrito.

O quadro 2 representa uma gramática para lista de dígitos separados por sinais de mais ou de menos.

#### QUADRO 2 – GRAMÁTICA DE OPERAÇÕES MATEMÁTICAS

Lista-> lista |sinal| dígito|&

Sinal-> +|

Dígito -> 0 | 1 | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9

# 4.3 TRADUÇÃO DIRIGIDA PELA SINTAXE

Segundo Aho (1995), pode se obter a tradução dirigida pela sintaxe, associando informações a uma construção de linguagem de programação atrelando os atributos aos símbolos gramaticais que representam a construção. Os valores para os atributos são computados através de regras semânticas associadas às produções da gramática.

A avaliação das regras semânticas pode gerar código, salvar informações numa tabela de símbolos, emitir mensagens de erro ou realizar quaisquer outras atividades.

O tópico seguinte apresentará um exemplo mais detalhado.

### 4.4 GRAMÁTICA PARA EXPRESSÕES LÓGICAS

Nas linguagens programação, inclusive na *Ladder*, as expressões lógicas são usadas para computar valores lógicos e também para fluxo de controle.

Segundo Aho (1995), as expressões lógicas são compostas por operadores lógicos (*and* (e), *or* (ou) e *not* (não)) aplicados a elementos que são variáveis lógicas ou expressões condicionais.

As expressões lógicas deste capítulo seguem a seguinte gramática.

### $E \rightarrow E$ or E/E and E| not E| true | false

Pode-se traduzir uma expressão lógica sem gerar qualquer código para quaisquer dos operadores lógicos e sem ter código para avaliar a expressão por inteiro. É possível se avaliar as expressões lógicas sem gerar código para os operadores lógicos se representar-se o valor de uma expressão por uma posição na seqüência do código.

Abaixo um esquema de tradução para expressões lógicas para uma linguagem com três operandos. Onde a esquerda está a regra de produção e a direita está regra semântica. Quando a expressão se encaixar na regra de produção o programa ativará a regra semântica correspondente.

TABELA 19 - ESQUEMA DE TRADUÇÃO PARA UM LINGUAGEM DE TRÊS OPERANDOS

| Produção                          | Regra semântica                                                 |

|-----------------------------------|-----------------------------------------------------------------|

| $E \rightarrow E_1$ or $E_2$      | {E.local:= novotemporario;                                      |

|                                   | <i>Emitir</i> ( $E.local$ ':=' $E_1.local$ 'or' $E_2.local$ )}  |

| $E \rightarrow E_1$ and $E_2$     | {E.local:= novotemporario;                                      |

|                                   | <i>Emitir</i> ( $E.local$ ':=' $E_1.local$ 'and' $E_2.local$ )} |

| $E \rightarrow \mathbf{not}  E_1$ | {E.local:= novotemporario;                                      |

|                                   | Emitir (E.local ':= not' $E_I$ .local)}                         |

| $E -> (E_I)$                      | $\{E.local:=E_{I}.local\}$                                      |

| E -> true                         | {E.local:=novo_temporário                                       |

|                                   | <i>Emitir (E.local ':= 1')}</i>                                 |

| E -> false                        | {E.local:=novo_temporário                                       |

|                                   | Emitir $(E.local ':= 0')$ }                                     |

A expressão (a **or** b) **and** (c **or** d), geraria a tradução apresentada no quadro 3. Ao encontrar a primeira operação OR o programa ativaria a regra semântica correspondente. Geraria um novo temporário indicado por T0 no código gerado abaixo na linha 1. Substituiria esta variável temporária no código continuando a tradução. Ao identificar a segunda operação OR geraria o temporário T1, e emitiria a linha 2. Substituiria a variável no código e continuaria. Ao encontrar a operação AND terminaria a tradução guardando o resultado na variável T2.

QUADRO 3 - TRADUÇÃO DA EXPRESSÃO (A OR B) AND (C OR D)

1: T0 := a or b (T0) **and** (c **or** d)

2: T1:= c or d (T0) **and** (T1)

3: T2:=T0 and T1

### 5 MPLAB

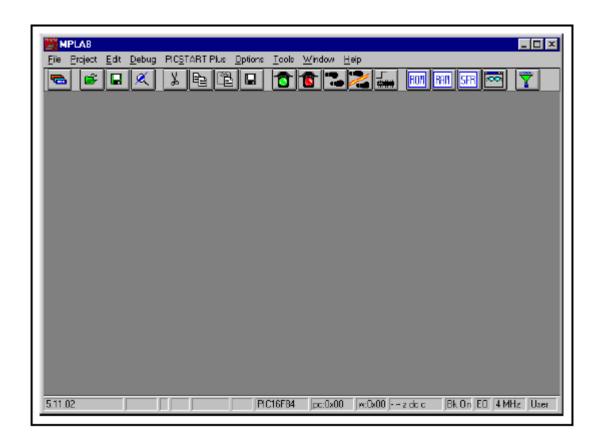

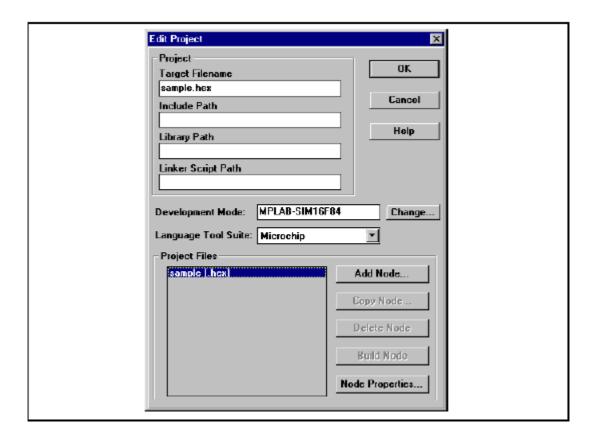

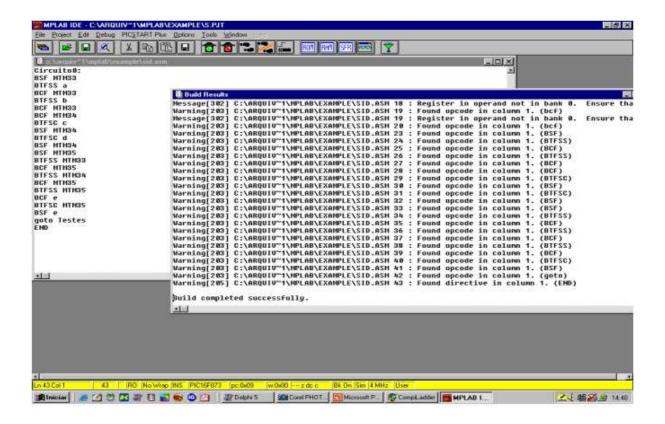

O MPLAB é uma ferramenta desenvolvida pela Microchip© para editar, simular e montar os códigos *assembly* para os microcontroladores fabricados pela empresa. A ferramenta possibilita editar o código através da edição de um arquivo texto. Este arquivo texto pode também ser compilado e pode ser testado passo-a-passo. A figura 10 exibe a interface do MPLAB.

FIGURA 10 - INTERFACE DO MPLAB

Para poder compilar e testar um programa assembly no MPLAB é necessário primeiramente criar um projeto. Para criar novo projeto clique em *Project/New Project* e salve com o nome que desejar.