# Implementação M++ em FPGA

Aluno(a): André L. Bieging

Orientador: Miguel A. Wisintainer

### Roteiro

- Introdução, objetivos;

- Fundamentação Teórica;

- Requisitos, especificação;

- Implementação;

- Operacionalidade;

- Resultados, conclusão.

# Introdução

Avanço dos semicondutores;

Diferentes tecnologias;

Possibilidade de um teste real.

## Objetivos

- Portar a M++ para um FPGA

- Carregar programas;

- Ler entradas e produzir saídas;

- Possibilidade de extensão da arquitetura;

- Material de ensino.

# Fundamentação Teórica

Verilog;

Quartus;

ModelSIM.

# Verilog - Módulos

```

module <module_name> (<module_terminal_list>);

...

<module internals>

...

endmodule

```

# Verilog – Entradas e Saídas

# Verilog - wire

```

module and_gate

in1,

in2,

out1

);

input in1, in2;

output out1;

wire and_temp;

assign and_temp = in1 & in2;

assign out1 = and_temp;

endmodule

```

# Verilog - reg

```

module and_gate

in1,

in2,

out1

);

input in1, in2;

output out1;

reg out1;

always @ (in1 or in2)

begin

out1 = in1 \& in2;

end

endmodule

```

# **Verilog - Delay**

```

always

begin

#10 clk = !clk;

end

```

# Verilog - initial

```

initial

begin

data = 8'b00000000;

end

```

# Verilog - always

```

always

begin

c1k = \sim c1k;

end

always @ (var1)

begin

out = var1;

end

always @ (posedge var1)

begin

out = var1;

end

always @ (var1 or var2)

begin

out = var1 & var2;

end

```

## Verilog – Sintaxe Variável

```

<tipo> [<tamanho>] <nome>;

reg [7:0] var1;

```

# **Verilog – Sintaxe Array**

```

<tipo> [<tamanho_vetor>] <nome> [<tamanho_array>];

reg [7:0] var1 [0:15];

```

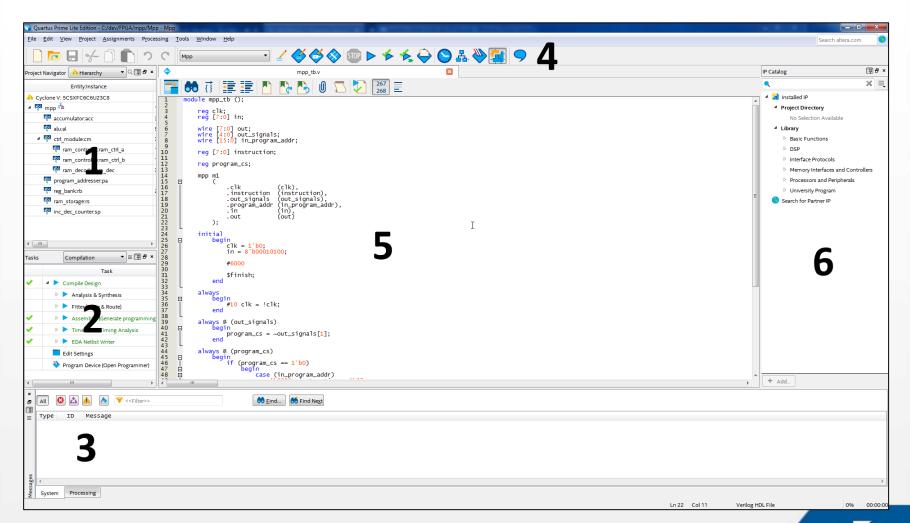

### Quartus

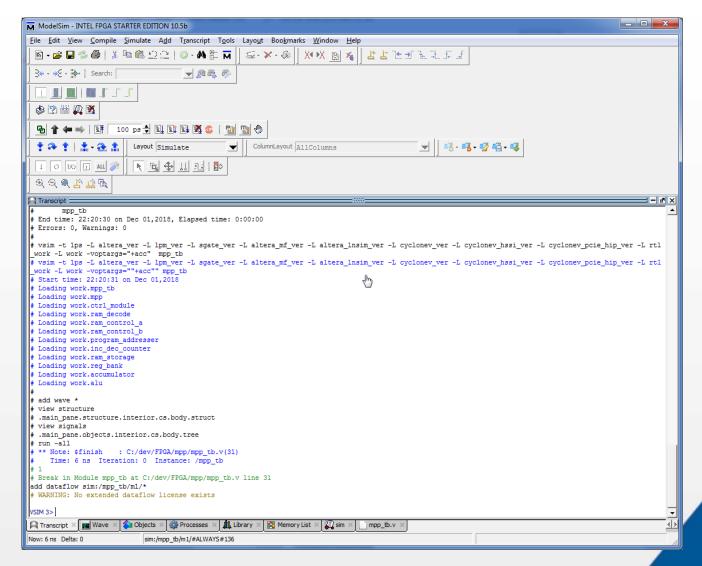

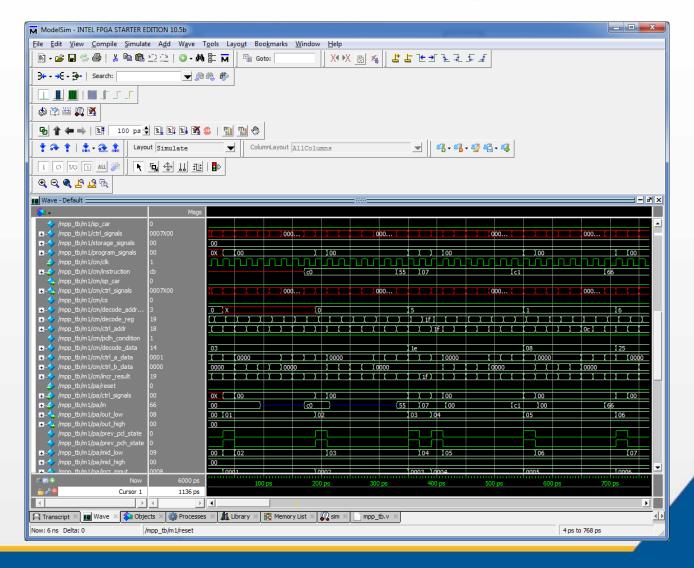

### **ModelSIM**

```

ModelSim - INTEL FPGA STARTER EDITION 10.5b

File Edit View Compile Simulate Add Source Tools Layout Bookmarks Window Help

□ · □ □ □ □ □ · M □ □ □ · M □ □ □ · M □ □

}• • • € • • Search:

w AR B

X X 🖹 🕺

👿 📗 🚜 - 🛂 - 🛂 - 🚭

Layout Simulate

🛨 🗫 🛊 🛣 - 👧 🛊

ColumnLayout Default

I O 1/O 🗍 ALL 🥢

C:/dev/FPGA/mpp/mpp_tb.v (/mpp_tb) - Default :

Ve I Now → I

.out signals (out signals),

19

.program_addr (in_program_addr),

20

.in

(in),

21

.out

(out)

22

);

23

24

initial

25

begin

26

clk = 1'b0;

27

in = 8'b00010100;

28

29

#6000

30

31 🗬

Sfinish:

32

end

33

34

always

35

begin

36

#10 clk = !clk;

37

end

38

39

always @ (out_signals)

40

begin

41

program cs = ~out signals[1];

42

end

43

44

always @ (program cs)

45

46

if (program cs == 1'b0)

case (in_program_addr)

49

'h0000: instruction = 'h07;

50

'h0001: instruction = 'hC0;

51

'h0002: instruction = 'h55:

52

'h0003: instruction = 'h07;

53

'h0004: instruction = 'hC1;

sim:/mpp_tb/#INITIAL#24

Ln: 23 Col: 0 READ

Now: 6 ns Delta: 0

```

### **ModelSIM**

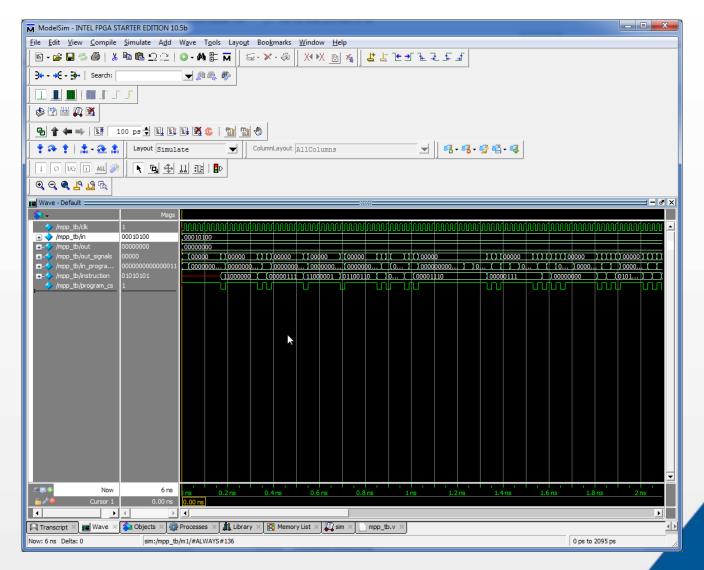

### **ModelSIM**

#### **Trabalhos Correlatos**

- FPGA IMPLEMENTATION OF AN 8-BIT SIMPLE PROCESSOR;

- A VERY SIMPLE 8-BIT RISC PROCESSOR FOR FPGA;

- DESIGN OF A GENERAL PURPOSE 8-BIT RISC PROCESSOR FOR COMPUTER ARCHITECTURE LEARNING.

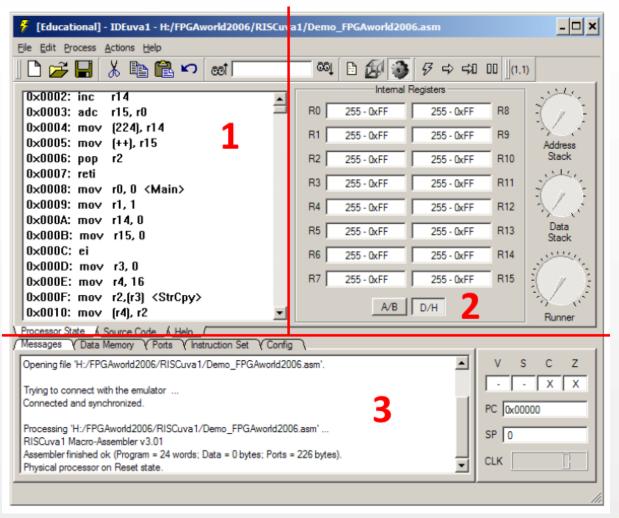

# FPGA IMPLEMENTATION OF AN 8-BIT SIMPLE PROCESSOR

Fonte: Ayeh et al., (2008).

# A VERY SIMPLE 8-BIT RISC PROCESSOR FOR FPGA

Fonte: PABLO et al., (2016).

# DESIGN OF A GENERAL PURPOSE 8-BIT RISC PROCESSOR FOR COMPUTER ARCHITECTURE LEARNING

Fonte: Zalava et al., (2015).

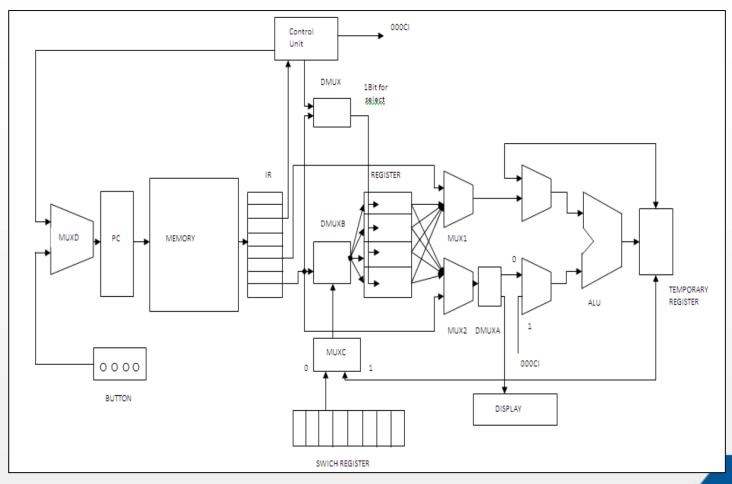

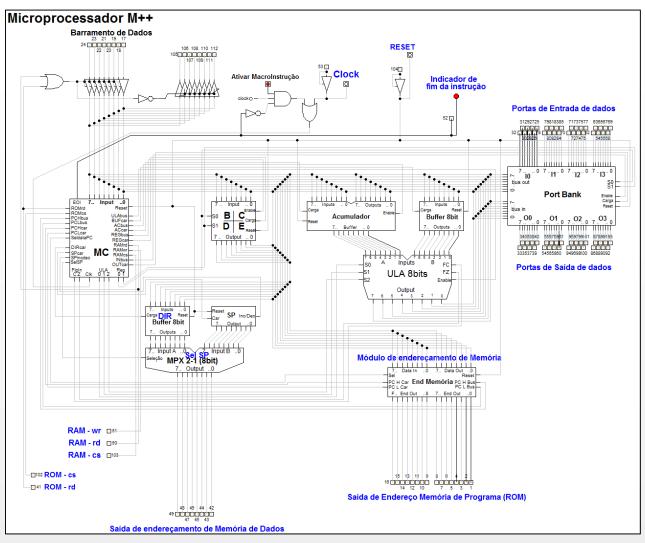

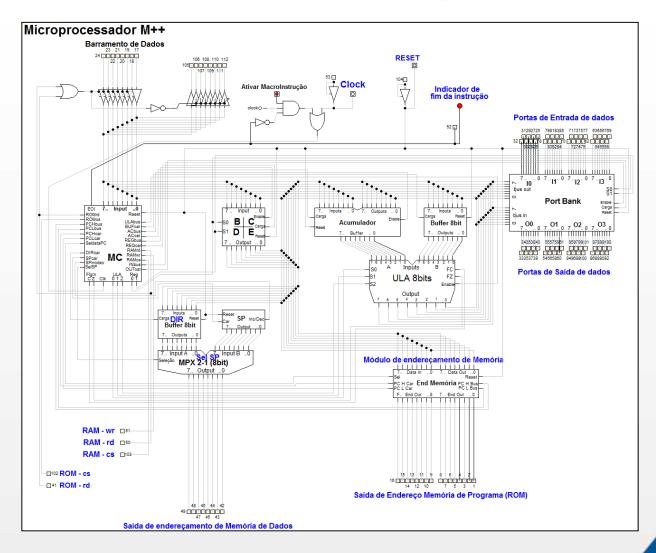

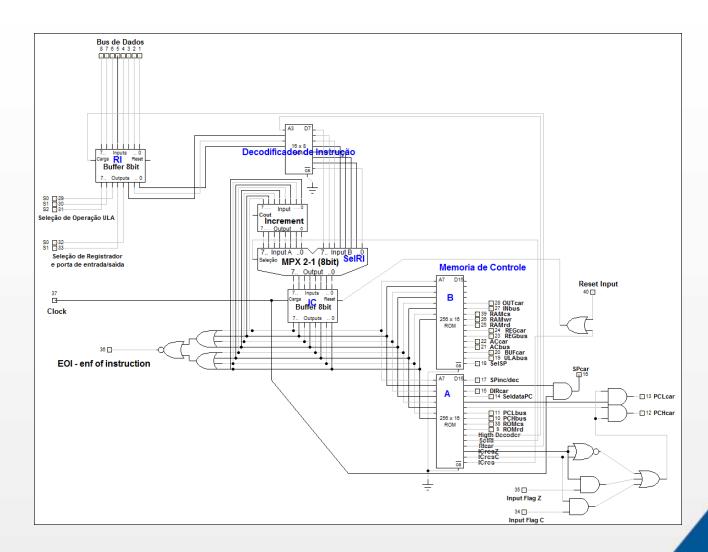

# **Arquitetura Atual**

- M++;

- CPU hipotética;

# **Arquitetura Atual**

Fonte: Borges (2003).

# Requisitos Funcionais

- RF1 armazenar programa em memória interna;

- RF2 ler programa armazenado em memória interna;

- RF3 ler entradas acionadas pelo usuário;

- RF4 acionar saídas conforme processamento do programa.

## Requisitos Não Funcionais

- RNF1 ser programado na linguagem de descrição de hardware Verilog no ambiente de programação Intel Quartus Prime;

- RNF2 ter a funcionalidade testada e comprovada com o software de simulação ModelSim\*-Intel® FPGA edition;

- RNF3 ser implementado em um kit de desenvolvimento da Altera, com um FPGA da família Cyclone V;

- RNF4 funcionar em um clock superior à 10KHz.

# Especificação

### Módulo de Controle

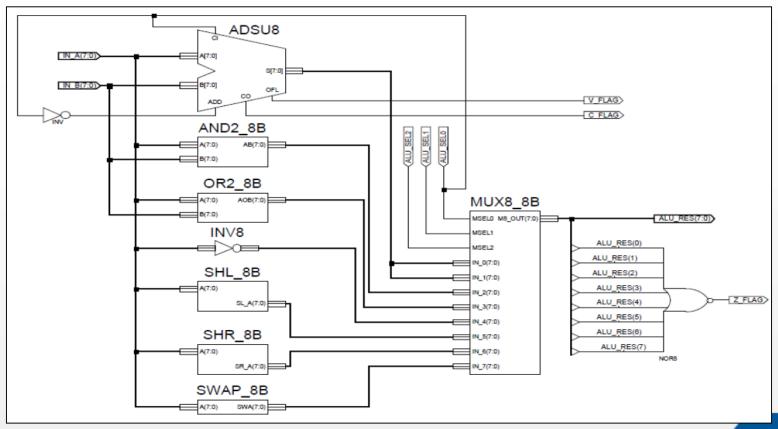

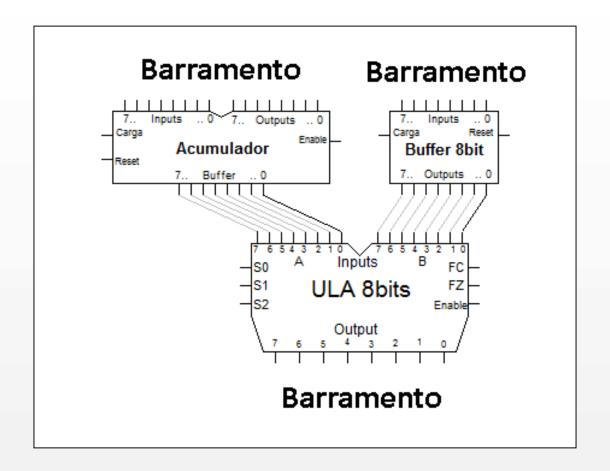

### **ULA**

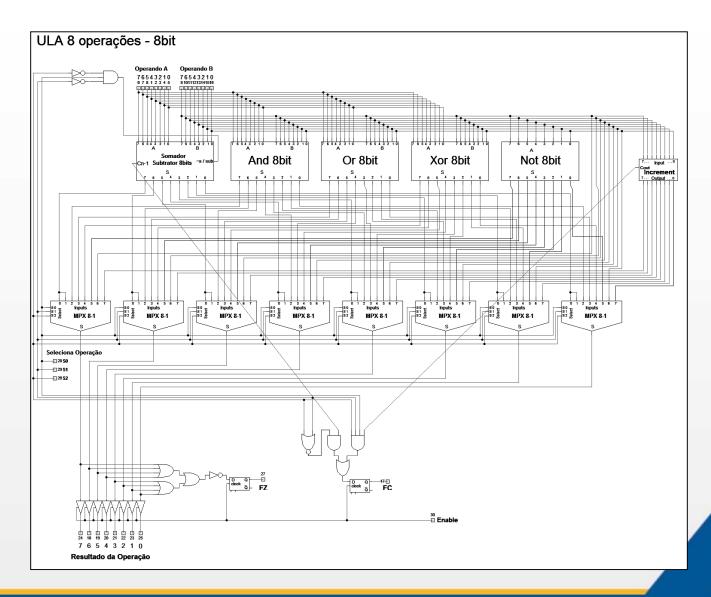

### **ULA - Interno**

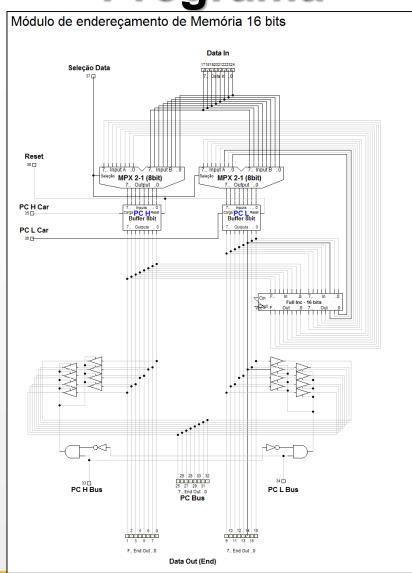

### Endereçador da Memória do Programa

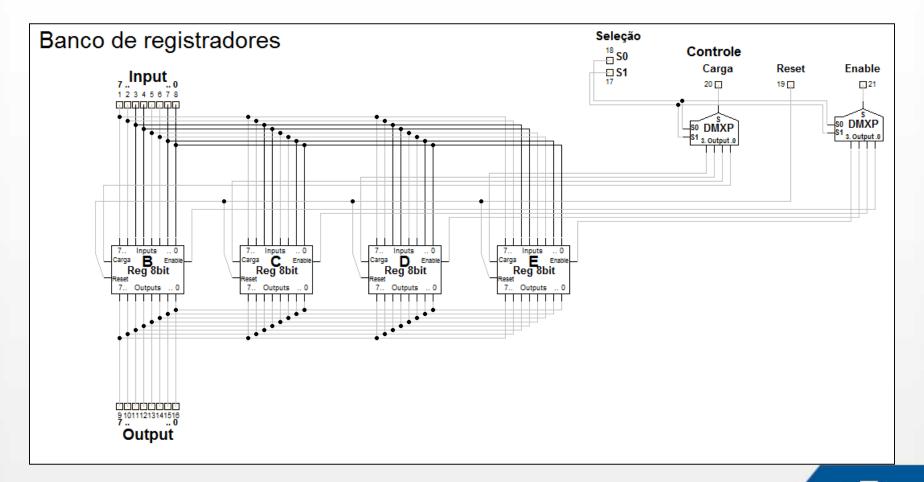

# Banco de Registradores

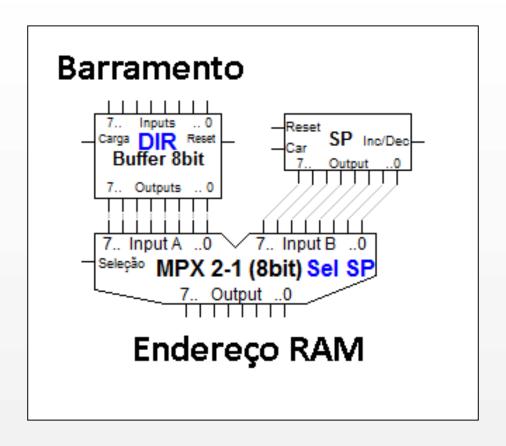

### Endereçador da Memória RAM

### **Call Stack**

loop: CALL SUBROT; JMP LOOP; SUBROT: RET;

### Implementação - Módulo M++

```

ctrl_module cm

(c1k),

.clk

.instruction

(instruction).

.ctrl_signals

(ctrl_signals),

(sp_car)

.sp_car

);

program_addresser pa

(program_signals),

.ctrl_signals

.reset

(reset),

.in

(bus).

(program_low),

.out_low

.out_high

(program_high)

);[

reg_bank rb

(reg_bank_sel).

.sel

(ctrl_signals[22]),

. en

(ctrl_signals[21]),

.load

.reset

(reset).

.in

(bus).

.out

(reg_bank_out)

);

accumulator acc

(ctrl_signals[24]),

. en

.load

(ctrl_signals[23]),

(reset),

.reset

.in

(bus),

.out

(acc_out).

.buffer (acc_buffer)

);

alu al

.sel

(alu_sel),

(ctrl_signals[26]),

. en

(acc_buffer),

.in_a

.in_b

(alu buffer).

.flag_c (alu_fc),

.flag_z (alu_fz),

.out

(alu_out)

```

### Módulo M++

```

always @ (*)

begin

if (out\_signals[0] == 1'b1)

begin

bus = instruction;

end

else if (storage_cs == 1'b1)

begin

bus = storage_data_out;

end

else if (ctrl_signals[2] == 1'bl)

begin

bus = program_high;

end

else if (ctrl_signals[3] == 1'b1)

begin

bus = program_low;

end

else if (ctrl_signals[22] == 1'b1)

begin

bus = req_bank_out;

end

else if (ctrl_signals[24] == 1'b1)

begin

bus = acc_out;

end

else if (ctrl_signals[26] == 1'b1)

begin

bus = alu_out;

end

else if (ctrl_signals[17] == 1'b1)

begin

bus = in;

end

end

```

```

always @ (posedge ctr]_a_data[3])

begin

decode_address[0] = instruction[0];

decode_address[1] = instruction[1];

decode_address[2] = instruction[2];

ctrl_signals[14] = instruction[3]; // REG0

ctrl_signals[15] = instruction[4]; // REG1

ctrl_signals[11] = instruction[5]; // ULA0

ctrl_signals[12] = instruction[6]; // ULA1

ctrl_signals[13] = instruction[7]; // ULA2

end

```

```

nor u1 (pclh_condition, ctrl_a_data[1], ctrl_a_data[2]);

always @ (ctrl_a_data or ctrl_b_data)

begin

// 4th address decoder signal.

decode_address[3] = ctrl_a_data[5];

// Control signals.

ctrl_signals[0] = ctrl_a_data[6]; //

ctrl_signals[1] = ctrl_a_data[7]; //

ctrl_signals[2] = ctrl_a_data[8]; // PCHbus

ctrl_signals[3] = ctrl_a_data[9]; // PCLbus

// PCHcar

if (ctrl_a_data[10] == 1'b1 \& pclh_condition == 1'b1)

beain

ctrl_signals[4] = 1'b1;

end

else

begin

ctrl_signals[4] = 1'b0;

end

// PCLcar

if (ctrl_a_data[11] == 1'b1 & pclh_condition == 1'b1)

begin

ctrl_signals[5] = 1'b1;

end

else

begin

ctrl_signals[5] = 1'b0;

end

// Reception of all other signals hidden.

#5 // Signals that have to wait to avoid race condition.

ctrl_signals[6] = ctrl_a_data[12]; // SelDataPC

end

```

## **ULA**

```

always @ (*)

begin

if (en == 1'b1)

begin

case (sel)

3'b000: out = in_a + in_b;

3'b001: out = in_a - in_b;

3'b010: out = in_a & in_b;

3'b011: out = in_a | in_b;

3'b100: out = in_a ^ in_b;

3'b101: out = !in_b;

3'b110: out = in_b;

3'b111: out = in_b + 1;

endcase

end

else

begin

out = 8'bzzzzzzzz;

end

end

```

# Endereçador da Memória do Programa

```

// Assigns.

assign incr_result = incr_input + 1;

// Always.

always @ (ctrl_signals)

begin

// Selection (SelDataPC).

if (ctrl_signals[0] == 1'b0)

begin

mid_low[0] = incr_result[0];

mid_low[1] = incr_result[1];

mid_low[2] = incr_result[2];

mid_low[3] = incr_result[3];

mid_low[4] = incr_result[4];

mid_low[5] = incr_result[5];

mid_low[6] = incr_result[6];

mid_low[7] = incr_result[7];

mid_high[0] = incr_result[8];

mid_high[1] = incr_result[9];

mid_high[2] = incr_result[10];

mid_high[3] = incr_result[11];

mid_high[4] = incr_result[12];

mid_high[5] = incr_result[13];

mid_high[6] = incr_result[14];

mid_high[7] = incr_result[15];

end

else

begin

mid_low[0] = in[0];

mid_low[1] = in[1];

mid_low[2] = in[2];

mid_low[3] = in[3];

mid_low[4] = in[4];

mid_low[5] = in[5];

mid_low[6] = in[6];

mid_low[7] = in[7];

mid_high[0] = in[0]:

mid_high[1] = in[1];

mid_high[2] = in[2];

mid_high[3] = in[3];

mid_high[4] = in[4];

mid_high[5] = in[5];

mid_high[6] = in[6];

mid_high[7] = in[7];

end

end

```

# Endereçador da Memória do Programa

```

/ Always.

always @ (ctrl_signals)

begin

// clock L (PCLcar).

if (ctrl_signals[2] == 1'b1 & prev_pcl_state == 1'b0)

begin

out_low = mid_low;

incr_input[0] = out_low[0];

incr_input[1] = out_low[1];

incr_input[2] = out_low[2];

incr_input[3] = out_low[3];

incr_input[4] = out_low[4]:

incr_input[5] = out_low[5];

incr_input[6] = out_low[6];

incr_input[7] = out_low[7];

end

prev_pcl_state = ctrl_signals[2];

// clock H (PCHcar).

if (ctrl_signals[1] == 1'b1 & prev_pch_state == 1'b0)

begin

out_low = mid_low;

incr_input[8] = out_high[0];

incr_input[9] = out_high[1];

incr_input[10] = out_high[2];

incr_input[11] = out_high[3];

incr_input[12] = out_high[4];

incr_input[13] = out_high[5];

incr_input[14] = out_high[6];

incr_input[15] = out_high[7];

end

prev_pch_state = ctrl_signals[1];

end

```

# Banco de Registradores

```

reg [7:0] regs [0:3];

integer i;

initial

begin

out = 8'b000000000;

for (i = 0; i < 4; i = i + 1)

begin

regs[i] = 8'b000000000;

end

end</pre>

```

# Banco de Registradores

```

always @ (sel or en or load or reset)

begin

if (en == 1'b1)

begin

out = regs[sel];

end

if (load == 1'b1)

begin

regs[sel] = in;

end

if (reset == 1'b1)

begin

for (i = 0; i < 4; i = i + 1)

begin

regs[i] = 8'b000000000;

end

end

end

```

# Endereçador da Memória RAM

```

initial

begin

out = 8'b00000000;

end

always @ (posedge set)

begin

if (reset == 1'b1)

beain

out = 8'b000000000:

end

else if (ctrl == 1'b0)

begin

out = out + 1:

end

else if (ctrl == 1'b1)

begin

out = out -1;

end

end

```

# Endereçador da Memória RAM

```

always @ (ctrl_signals)

begin

storage_rw = ctrl_signals[20]; // RAMrd

// DIR buffer.

if (ctrl_signals[7] == 1'b1)

begin

dir_sp_buffer = bus;

end

// Sel SP MUX.

if (ctrl\_signals[10] == 1'b0)

begin

storage_addr = dir_sp_buffer;

end

else

begin

storage_addr = storage_signals;

end

if (ctrl_signals[16] == 1'b1)

begin

out <= bus:

end

#5

storage_cs = ctrl_signals[18]; // RAMcs

#10

storage_cs = 0; // RAMcs

end

```

### Memórias ROM

```

module ram_decode

addr.

data

):

input en;

input [3:0] addr;

output [7:0] data;

reg [7:0] data;

initial

begin

data = 8'b000000000:

end

always @ (addr)

begin

if (en == 1'b0)

begin

case (addr)

4'b0000: data = 8'b00000011;

4'b0001: data = 8'b00001000;

4'b0010: data = 8'b00001101;

4'b0011: data = 8'b00010100:

4'b0100: data = 8'b00011001;

4'b0101: data = 8'b00011110;

4'b0110: data = 8'b00100101;

4'b0111: data = 8'b00101010:

4'b1000: data = 8'b00101100;

4'b1001: data = 8'b00110001;

4'b1010: data = 8'b00110110;

4'b1011: data = 8'b00111101:

4'b1100: data = 8'b01000110:

4'b1101: data = 8'b01010000;

4'b1110: data = 8'b01011001;

4'b1111: data = 8'b01101100:

endcase

end

end

endmodule

```

### Memórias ROM

```

always @ (program_cs)

begin

if (program_cs == 1'b0)

begin

case (in_program_addr)

'h0000: instruction = 'h07;

'h0001: instruction = 'hC0;

'h0002: instruction = 'h55;

'h0003: instruction = 'h07;

'h0004: instruction = 'hC1;

'h0005: instruction = 'h66;

'h0006: instruction = 'h07:

'h0007: instruction = 'h06;

'h0008: instruction = 'h00;

'h0009: instruction = 'h0E:

'h000A: instruction = 'h07;

'h000B: instruction = 'h03;

'h000c: instruction = 'h00:

'h000D: instruction = 'h00;

'h000E: instruction = 'h04;

'h000F: instruction = 'h07;

'h0010: instruction = 'h07:

endcase

end

end

```

#### Bloco de Estímulo

```

module mpp_tb ();

reg clk;

reg [7:0] in;

wire [7:0] out;

wire [4:0] out_signals;

wire [15:0] in_program_addr;

reg [7:0] instruction;

reg program_cs;

mpp m1

.clk

(c1k),

.instruction (instruction),

.out_signals

(out_signals),

(in_program_addr).

.program_addr

.in

(in),

(out)

. out

);

```

### Bloco de Estímulo

```

initial

begin

clk = 1'b0;

in = 8'b00010100;

#6000

$finish;

end

```

#### Bloco de Estímulo

```

always

beain

#10 clk = !clk;

end

always @ (out_signals)

begin

program_cs = ~out_signals[1];

end

always @ (program_cs)

begin

if (program_cs == 1'b0)

begin

case (in_program_addr)

'h0000: instruction = 'h07;

'h0001: instruction = 'hC0;

'h0002: instruction = 'h55;

'h0003: instruction = 'h07;

'h0004: instruction = 'hC1;

'h0005: instruction = 'h66;

'h0006: instruction = 'h07;

'h0007: instruction = 'h06;

'h0008: instruction = 'h00;

'h0009: instruction = 'h0E:

'h000A: instruction = 'h07;

'h000B: instruction = 'h03;

'h000C: instruction = 'h00;

'h000D: instruction = 'h00;

'h000E: instruction = 'h04;

'h000F: instruction = 'h07:

'h0010: instruction = 'h07;

endcase

end

end

```

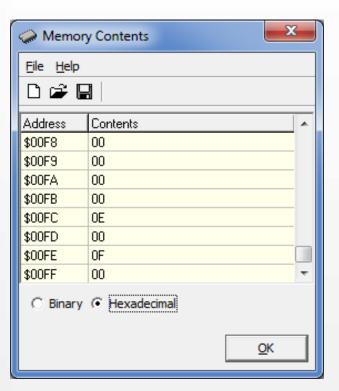

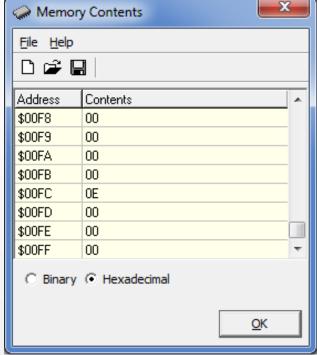

# Operacionalidade da Implementação

```

loop:

MOV 55,A;

MOV 66,B;

ADD B,A;

MOV A,B;

MOV A,OUT1;

CALL MOVE;

JMP LOOP;

MOVE:

RET:

```

# Operacionalidade da Implementação

# Comparação Correlatos

| correlatos           | AYEH et     | PABLO et    | ZALAVA   | M++     |

|----------------------|-------------|-------------|----------|---------|

|                      | al., (2008) | al., (2016) | et al.,  | FPGA    |

| características      |             |             | (2015)   |         |

| fabricante           | Xilinx      | Xilinx      | Xilinx   | Altera  |

| tecnologia           | FPGA        | FPGA        | FPGA     | FPGA    |

| número de instruções | 4           | 29          | 29       | 14      |

| arquitetura          | Própria     | Harvard     | Harvard  | Harvard |

| set de instruções    | Próprio     | RISC        | RISC     | Próprio |

| frequência           | ~95MHz      | ~40MHz      | Não inf. | 90MHz   |

#### Resultados e Discussões

- 90MHz teóricos;

- 129 elementos lógicos (<1%);

- Arquitetura funciona corretamente.

#### Conclusões

- Objetivos atendidos;

- Importante para a área;

- Prova real da arquitetura;

- Limitações.

#### Extensões

- M+++;

- RISC;

- Otimização;

- Barramento de 16 bits;

- Melhorias no código;

- Open Source;

- Documentação;

- Interface externa.

### Referências

- AYEH, Eric et al. FPGA Implementation of an 8-bit Simple Processor.

Denton, [2008]. Disponível em:

<a href="https://www.researchgate.net/publication/4342279">https://www.researchgate.net/publication/4342279</a>. Acesso em: 4 abril 2018.

- BORGES, Jonathan M.. CONSTRUÇÃO DE UMA UCP HIPOTÉTICA M++.

Blumenau, [2003]. Disponível em:

<a href="http://www.inf.furb.br/~maw/mmaismais/artigos/artigo.pdf">http://www.inf.furb.br/~maw/mmaismais/artigos/artigo.pdf</a>>. Acesso em: 6

abril 2018.

- PABLO, S. de. et al. A very simple 8-bit RISC processor for FPGA.

Valladolid, [2016]. Disponível em:

<a href="https://www.researchgate.net/publication/267766934">https://www.researchgate.net/publication/267766934</a>. Acesso em: 4 abril 2018.

- Zavala, Antonio H. et al. Design of a General Purpose 8-bit RISC Processor for Computer Architecture Learning. Querétaro, [2015]. Disponível em: <a href="http://www.scielo.org.mx/pdf/cys/v19n2/v19n2a13.pdf">http://www.scielo.org.mx/pdf/cys/v19n2/v19n2a13.pdf</a>>. Acesso em: 4 abril 2018.

# Obrigado!